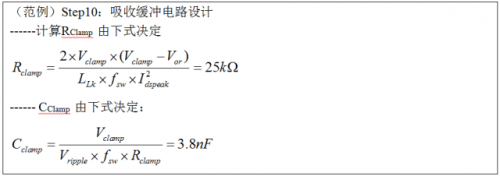

11. Step11:补偿电路设计

开关电源系统是典型的闭环控制系统,设计时,补偿电路的调试占据了相当大的工作量。目前流行于市面上的反激控制器,绝大多数采用峰值电流控制控制模式。峰值电流模式反激的功率级小信号可以简化为一阶系统,所以它的补偿电路容易设计。通常,使用 Dean Venable 提出的 Type II 补偿电路就足够了。

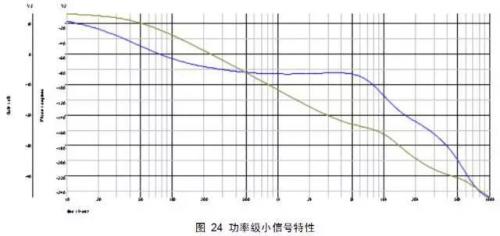

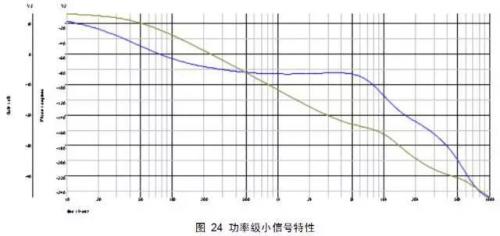

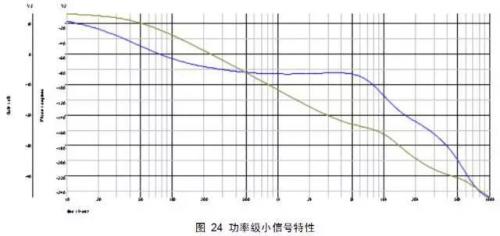

在设计补偿电路之前,首先需要考察补偿对象(功率级)的小信号特性。

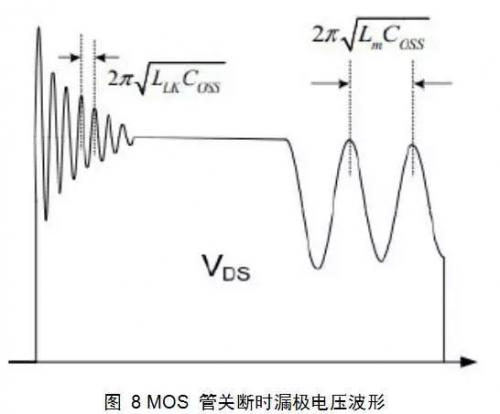

如图 8 所示,从 IC 内部比较器的反相端断开,则从控制到输出的传递函数(即控制对象的传递函数)为:

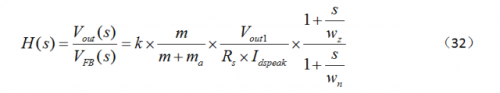

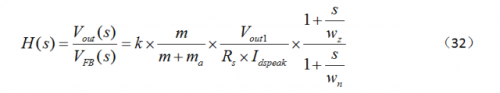

附录分别给出了 CCM 模式和 DCM 模式反激变换器的功率级传递函数模型。NCP1015 工作在 DCM 模式,从控制到输出的传函为:

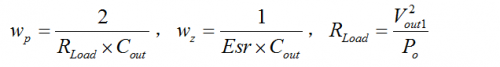

其中:

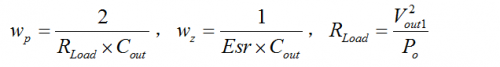

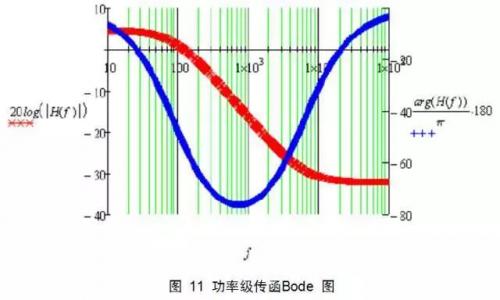

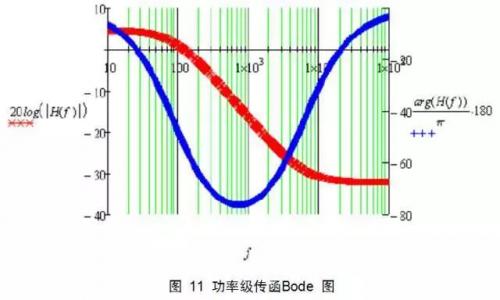

Vout1 为主路输出直流电压,k 为误差放大器输出信号到电流比较器输入的衰减系数(对 NCP1015 而言,k=0.25),m 为初级电流上升斜率,ma 为斜坡补偿的补偿斜率(由于 NCP1015 内部没有斜坡补偿,即 ma=0),Idspeak 为给定条件下初级峰值电流。于是我们就可以使用 Mathcad(或 Matlab)绘制功率级传函的 Bode 图:

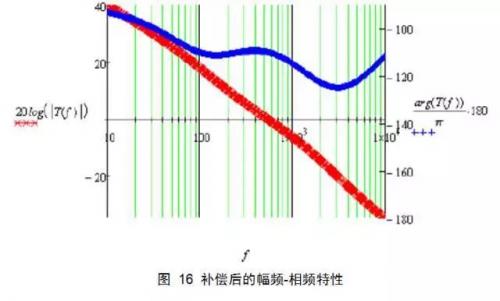

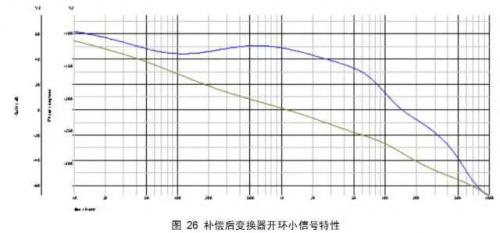

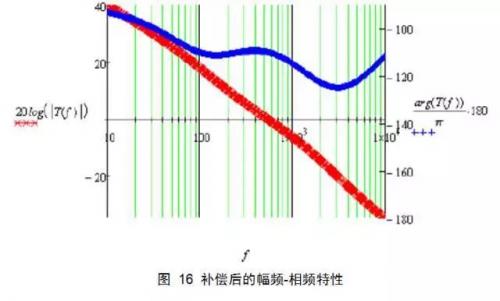

在考察功率级传函 Bode 图的基础上,我们就可以进行环路补偿了。

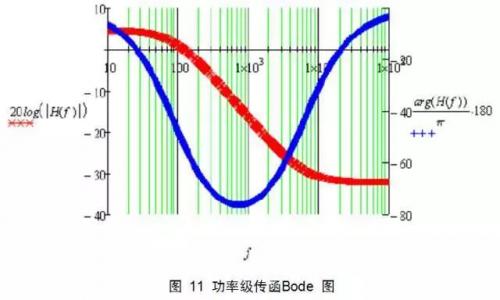

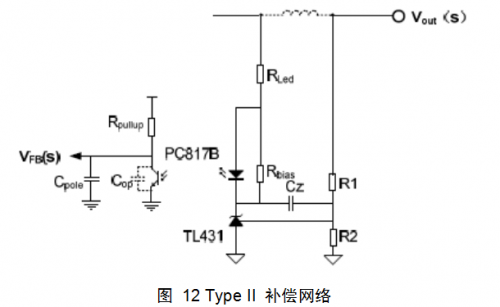

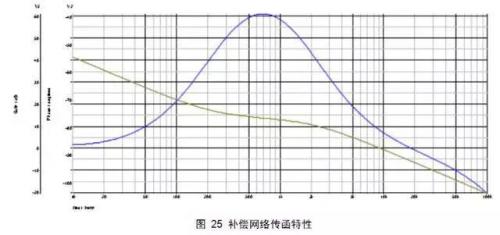

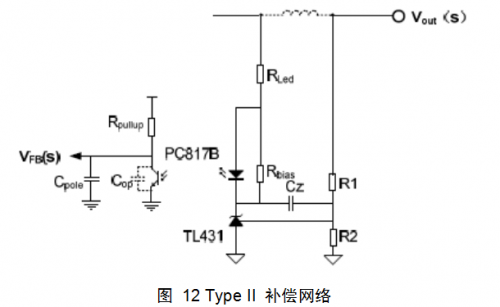

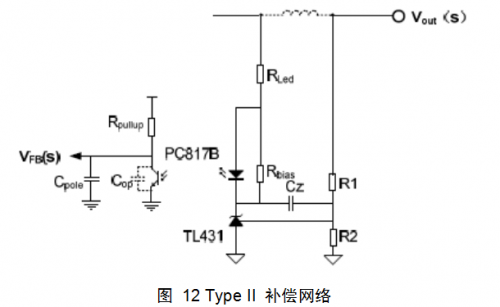

前文提到,对于峰值电流模式的反激变换器,使用 Dean Venable Type II 补偿电路即可,典型的接线方式如下图所示:

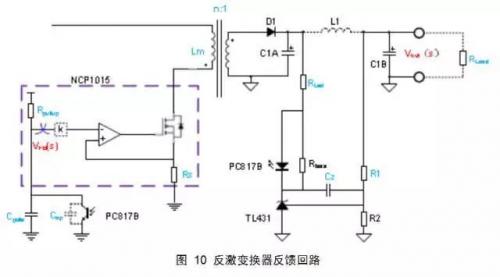

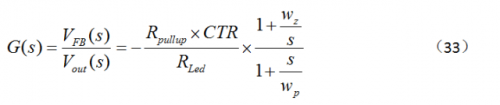

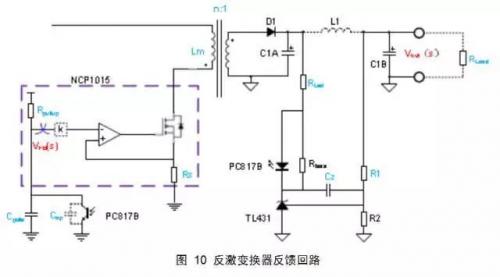

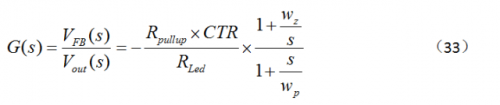

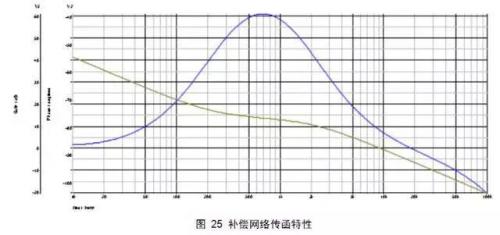

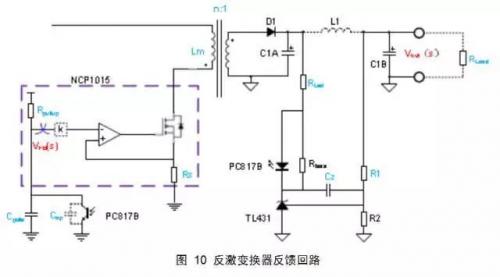

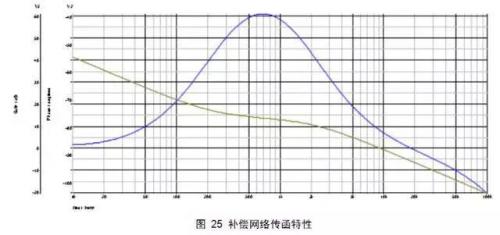

通常,为降低输出纹波噪声,输出端会加一个小型的 LC 滤波器,如图 10 所示,L1、C1B 构成的二阶低通滤波器会影响到环路的稳定性,L1、C1B 的引入,使变换器的环路分析变得复杂,不但影响功率级传函特性,还会影响补偿网络的传函特性。然而,建模分析后可知:如果 L1、C1B 的转折频率大于带宽 fcross 的 5 倍以上,那么其对环路的影响可以忽略不计,实际设计中,建议 L1 不超过 4.7μH。于是我们简化分析时,直接将 L1 直接短路即可,推导该补偿网络的传递函数 G(s)为:

其中:

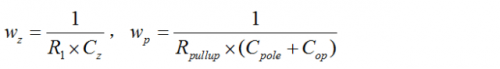

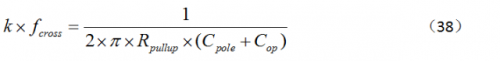

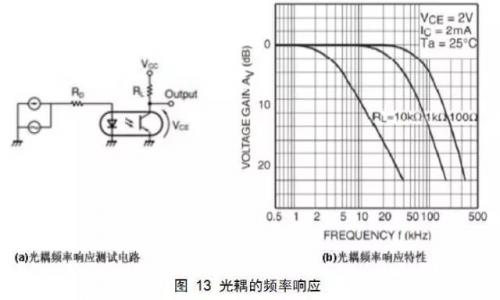

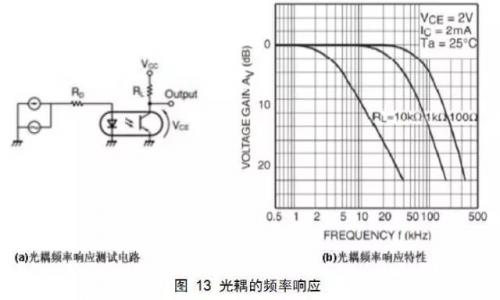

CTR 为光耦的电流传输比,Rpullup 为光耦次级侧上拉电阻(对应 NCP1015,Rpullup=18kΩ),Cop 为光耦的寄生电容,与 Rpullup 的大小有关。图 13(来源于 Sharp PC817 的数据手册)是光耦的频率响应特性,可以看出,当 RL(即 Rpullup)为 18kΩ时,将会带来一个约 2kHz 左右的极点,所以 Rpullup 的大小会直接影响到变换器的带宽。

k Factor(k 因子法)是 Dean Venable 在 20 世纪 80 年代提出来的,提供了一种确定补偿网络参数的方法。

如图 14 所示,将 Type II 补偿网络的极点 wp 放到 fcross 的 k 倍处,将零点 wz 放到 fcross 的 1/k 处。图 12 的补偿网络有三个参数需要计算:RLed,Cz,Cpole,下面将用 k Factor 计算这些参数:

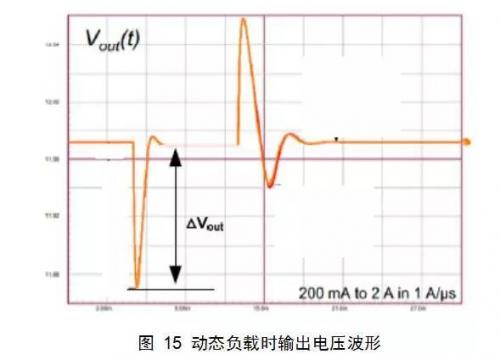

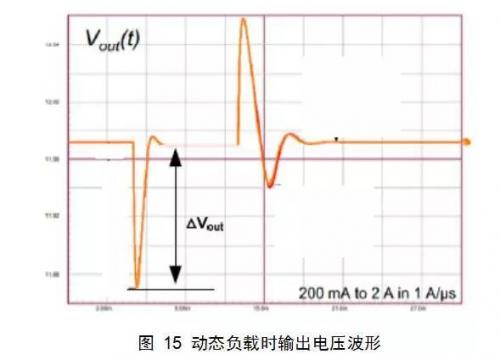

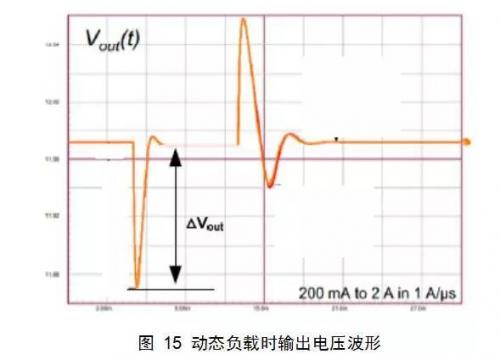

------- 确定补偿后的环路带宽 fcross:通过限制动态负载时(△Iout)的输出电压过冲量(或下冲量)△Vout,由下式决定环路带宽:

------- 考察功率级的传函特性,确定补偿网络的中频带增益(Mid-band Gain):

------- 确定 Dean Venable 因子 k:选择补偿后的相位裕量 PM(一般取 55°~80°),由公式 32 得到 fcross 处功率级的相移(可由 Mathcad 计算)PS,则补偿网络需要提升的相位 Boost 为:

则 k 由下式决定:

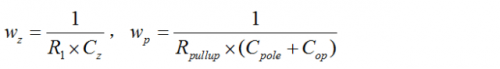

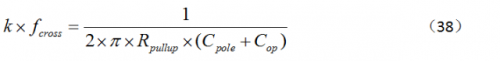

------- 补偿网络极点(wp)放置于 fcross 的 k 倍处,可由下式计算出 Cpole:

------- 补偿网络零点(wz)放置于 fcross 的 1/k 倍处,可由下式计算出 Cz:

仿真验证

计算机仿真不仅可以取代系统的许多繁琐的人工分析,减轻劳动强度,避免因为解析法在近似处理中带来的较大误差,还可以与实物调试相互补充,最大限度的降低设计成本,缩短开发周期。

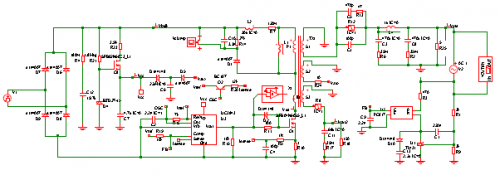

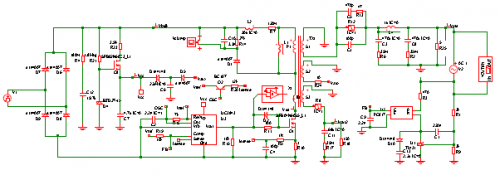

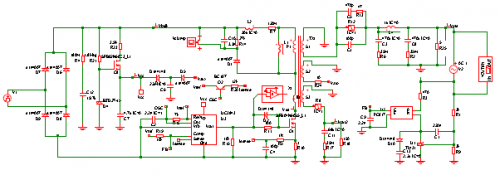

本例采用经典的电流型控制器 UC3843(与 NCP1015 控制原理类似),搭建反激变换器。其中,变压器和环路补偿参数均采用上文的范例给出的计算参数。

仿真测试条件:低压输入(90VAC,双路满载)

1. 原理图

图 17 仿真原理图

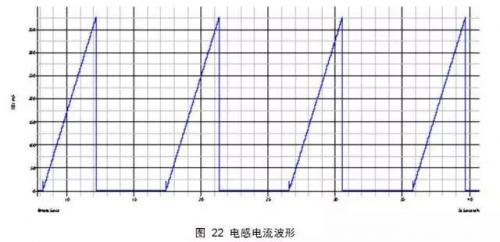

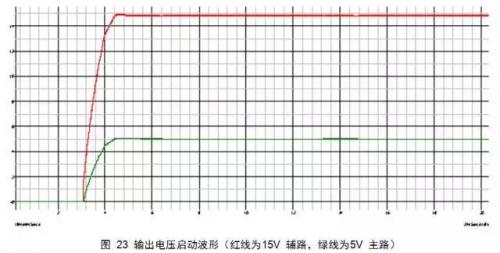

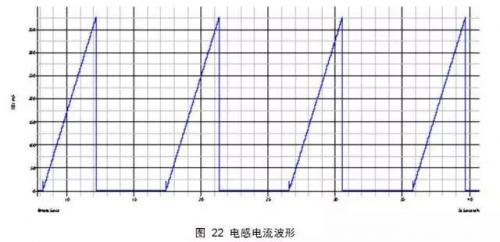

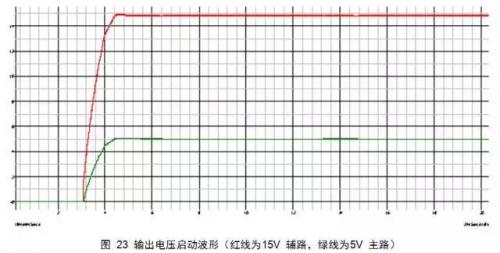

2. 瞬态信号时域分析

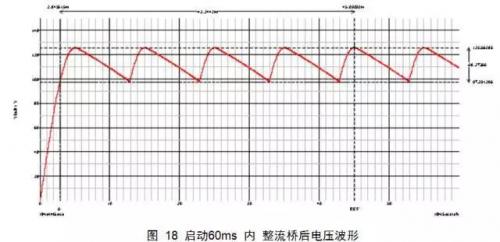

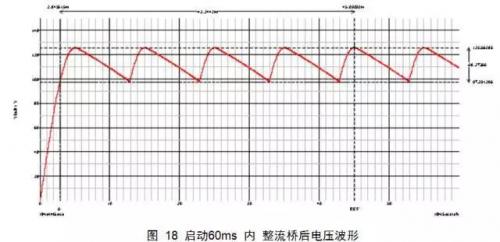

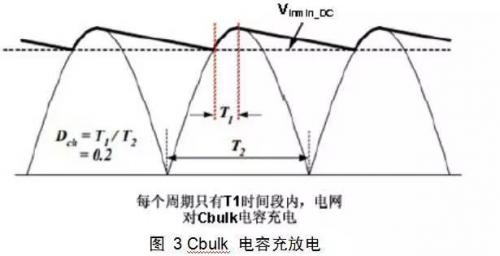

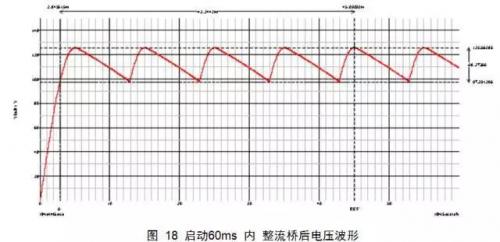

从图 18 可以看出,最低 Cbulk 上的最低电压为 97.3V,与理论值 98V 大致相符。

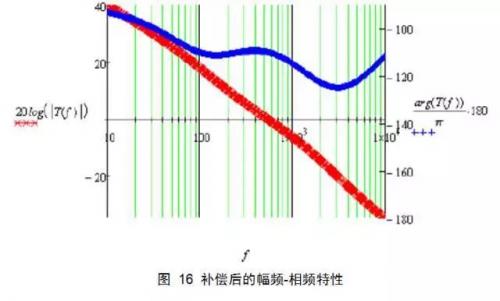

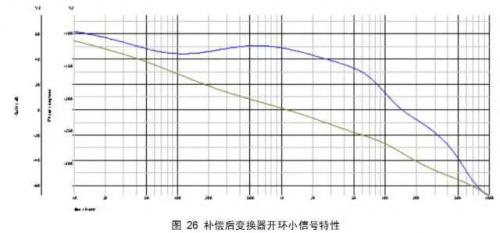

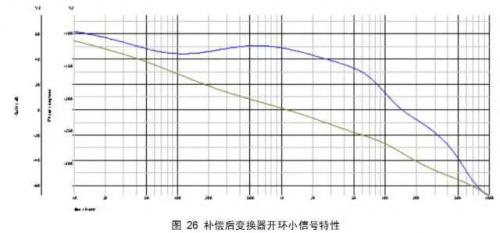

3. 交流信号频域分析

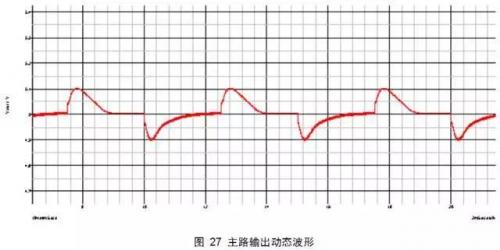

4. 动态负载波形测试

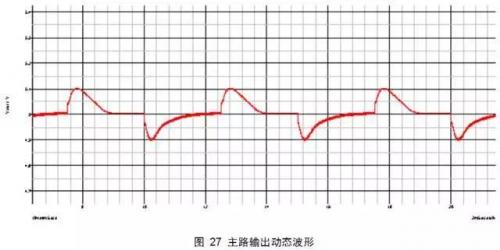

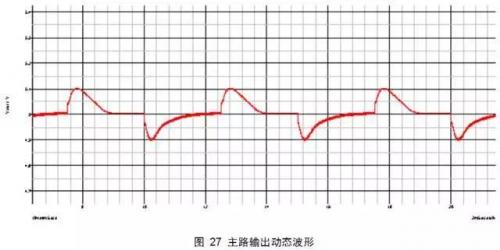

测试条件:低压输入,满载,主路输出电流 0.1A---1A---0.1A,间隔 2.5ms,测试输出电压波形。

PCB 设计指导

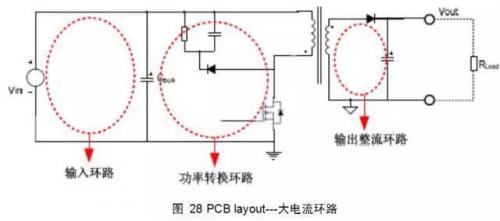

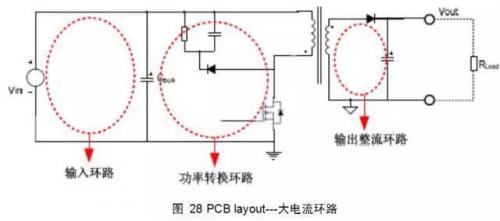

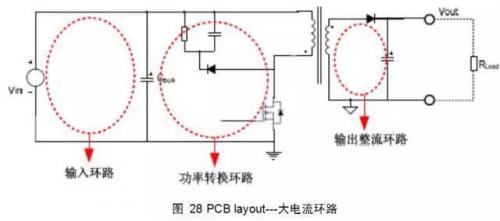

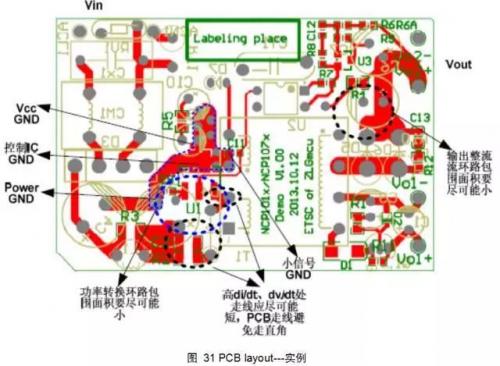

1. PCB layout—大电流环路

大电流环路包围的面积应极可能小,走线要宽。

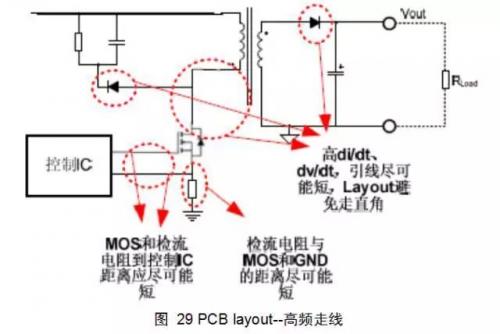

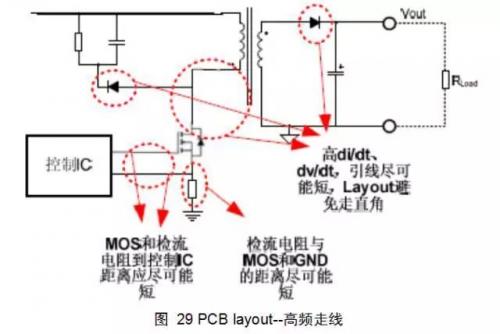

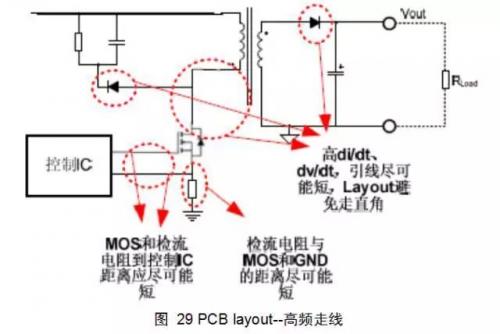

2. PCB layout—高频(di/dt、dv/dt)走线

a. 整流二级,钳位吸收二极管,MOS 管与变压器引脚,这些高频处,引线应尽可能短,layout 时避免走直角;

b. MOS 管的驱动信号,检流电阻的检流信号,到控制 IC 的走线距离越短越好;

c. 检流电阻与 MOS 和 GND 的距离应尽可能短。

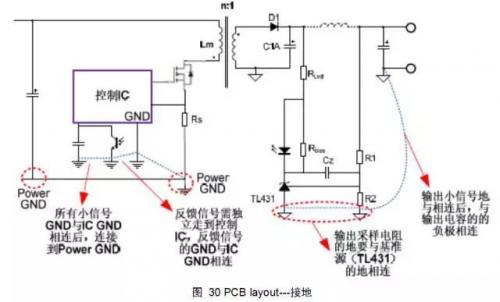

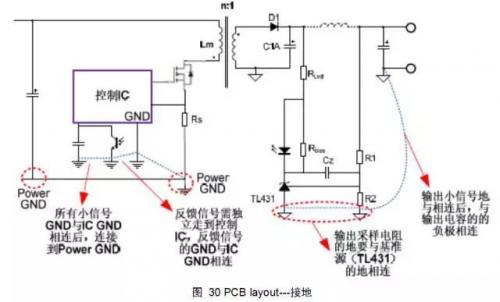

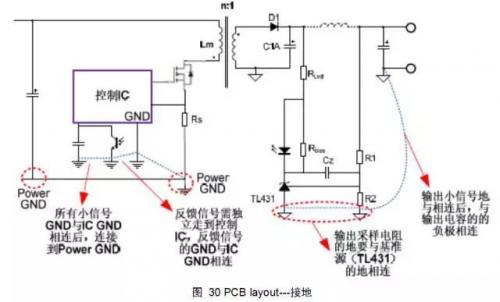

3. PCB layout—接地

初级接地规则:

a. 所有小信号 GND 与控制 IC 的 GND 相连后,连接到 Power GND(即大信号 GND);

b. 反馈信号应独立走到 IC,反馈信号的 GND 与 IC 的 GND 相连。

次级接地规则:

a. 输出小信号地与相连后,与输出电容的的负极相连;

b. 输出采样电阻的地要与基准源(TL431)的地相连。

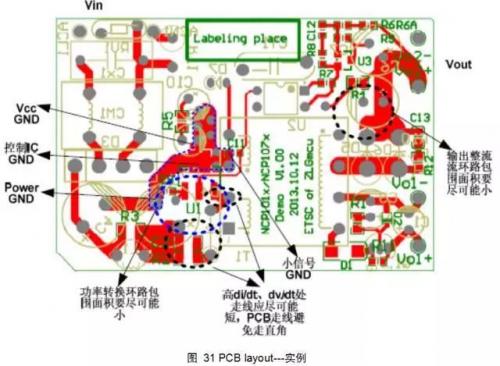

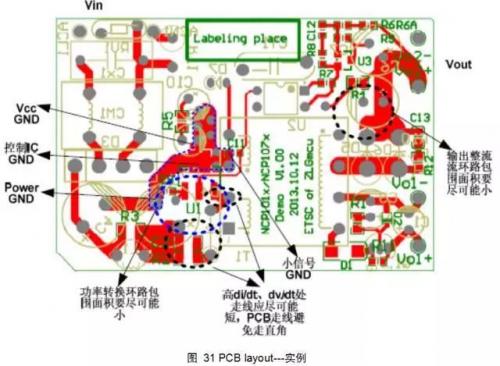

PCB layout—实例

11. Step11:补偿电路设计

开关电源系统是典型的闭环控制系统,设计时,补偿电路的调试占据了相当大的工作量。目前流行于市面上的反激控制器,绝大多数采用峰值电流控制控制模式。峰值电流模式反激的功率级小信号可以简化为一阶系统,所以它的补偿电路容易设计。通常,使用 Dean Venable 提出的 Type II 补偿电路就足够了。

在设计补偿电路之前,首先需要考察补偿对象(功率级)的小信号特性。

如图 8 所示,从 IC 内部比较器的反相端断开,则从控制到输出的传递函数(即控制对象的传递函数)为:

附录分别给出了 CCM 模式和 DCM 模式反激变换器的功率级传递函数模型。NCP1015 工作在 DCM 模式,从控制到输出的传函为:

其中:

Vout1 为主路输出直流电压,k 为误差放大器输出信号到电流比较器输入的衰减系数(对 NCP1015 而言,k=0.25),m 为初级电流上升斜率,ma 为斜坡补偿的补偿斜率(由于 NCP1015 内部没有斜坡补偿,即 ma=0),Idspeak 为给定条件下初级峰值电流。于是我们就可以使用 Mathcad(或 Matlab)绘制功率级传函的 Bode 图:

在考察功率级传函 Bode 图的基础上,我们就可以进行环路补偿了。

前文提到,对于峰值电流模式的反激变换器,使用 Dean Venable Type II 补偿电路即可,典型的接线方式如下图所示:

通常,为降低输出纹波噪声,输出端会加一个小型的 LC 滤波器,如图 10 所示,L1、C1B 构成的二阶低通滤波器会影响到环路的稳定性,L1、C1B 的引入,使变换器的环路分析变得复杂,不但影响功率级传函特性,还会影响补偿网络的传函特性。然而,建模分析后可知:如果 L1、C1B 的转折频率大于带宽 fcross 的 5 倍以上,那么其对环路的影响可以忽略不计,实际设计中,建议 L1 不超过 4.7μH。于是我们简化分析时,直接将 L1 直接短路即可,推导该补偿网络的传递函数 G(s)为:

其中:

CTR 为光耦的电流传输比,Rpullup 为光耦次级侧上拉电阻(对应 NCP1015,Rpullup=18kΩ),Cop 为光耦的寄生电容,与 Rpullup 的大小有关。图 13(来源于 Sharp PC817 的数据手册)是光耦的频率响应特性,可以看出,当 RL(即 Rpullup)为 18kΩ时,将会带来一个约 2kHz 左右的极点,所以 Rpullup 的大小会直接影响到变换器的带宽。

k Factor(k 因子法)是 Dean Venable 在 20 世纪 80 年代提出来的,提供了一种确定补偿网络参数的方法。

如图 14 所示,将 Type II 补偿网络的极点 wp 放到 fcross 的 k 倍处,将零点 wz 放到 fcross 的 1/k 处。图 12 的补偿网络有三个参数需要计算:RLed,Cz,Cpole,下面将用 k Factor 计算这些参数:

------- 确定补偿后的环路带宽 fcross:通过限制动态负载时(△Iout)的输出电压过冲量(或下冲量)△Vout,由下式决定环路带宽:

------- 考察功率级的传函特性,确定补偿网络的中频带增益(Mid-band Gain):

------- 确定 Dean Venable 因子 k:选择补偿后的相位裕量 PM(一般取 55°~80°),由公式 32 得到 fcross 处功率级的相移(可由 Mathcad 计算)PS,则补偿网络需要提升的相位 Boost 为:

则 k 由下式决定:

------- 补偿网络极点(wp)放置于 fcross 的 k 倍处,可由下式计算出 Cpole:

------- 补偿网络零点(wz)放置于 fcross 的 1/k 倍处,可由下式计算出 Cz:

仿真验证

计算机仿真不仅可以取代系统的许多繁琐的人工分析,减轻劳动强度,避免因为解析法在近似处理中带来的较大误差,还可以与实物调试相互补充,最大限度的降低设计成本,缩短开发周期。

本例采用经典的电流型控制器 UC3843(与 NCP1015 控制原理类似),搭建反激变换器。其中,变压器和环路补偿参数均采用上文的范例给出的计算参数。

仿真测试条件:低压输入(90VAC,双路满载)

1. 原理图

图 17 仿真原理图

2. 瞬态信号时域分析

从图 18 可以看出,最低 Cbulk 上的最低电压为 97.3V,与理论值 98V 大致相符。

3. 交流信号频域分析

4. 动态负载波形测试

测试条件:低压输入,满载,主路输出电流 0.1A---1A---0.1A,间隔 2.5ms,测试输出电压波形。

PCB 设计指导

1. PCB layout—大电流环路

大电流环路包围的面积应极可能小,走线要宽。

2. PCB layout—高频(di/dt、dv/dt)走线

a. 整流二级,钳位吸收二极管,MOS 管与变压器引脚,这些高频处,引线应尽可能短,layout 时避免走直角;

b. MOS 管的驱动信号,检流电阻的检流信号,到控制 IC 的走线距离越短越好;

c. 检流电阻与 MOS 和 GND 的距离应尽可能短。

3. PCB layout—接地

初级接地规则:

a. 所有小信号 GND 与控制 IC 的 GND 相连后,连接到 Power GND(即大信号 GND);

b. 反馈信号应独立走到 IC,反馈信号的 GND 与 IC 的 GND 相连。

次级接地规则:

a. 输出小信号地与相连后,与输出电容的的负极相连;

b. 输出采样电阻的地要与基准源(TL431)的地相连。

PCB layout—实例

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报