前端

电路设计提供一个-1v~1v的信号,其实是一个小信号(mv级)。

在AD采样的模拟输入端,能够看到AD20MHz 的时钟串入AD的模拟输入端。而且p-p有200mv。

模拟输入和时钟输入都是lvds标准的。

PCB上的布线也是等长的。

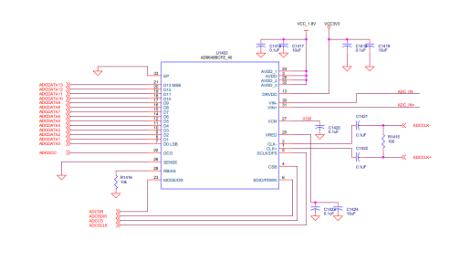

外围电路都是按照ADC的参考电路设计的。

有一个问题是

FPGA用的是altera的EP4CE15F17,里面给ADC的时钟标准是LVDS_E_3R,不是LVDS。当时设计的时候没有注意加上电阻网络

这个会使ADC时钟串扰到模拟输入端吗?

是芯片问题还是FPGA问题?

举报

举报