作者:王烈洋 黄小虎 占连样 珠海欧比特控制工程股份有限公司

随着

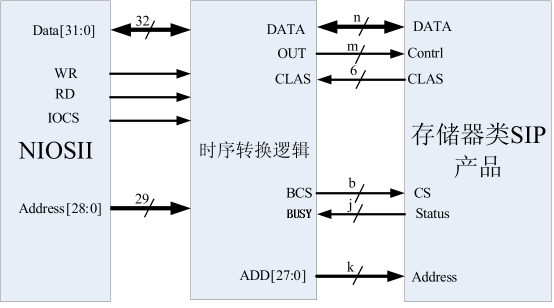

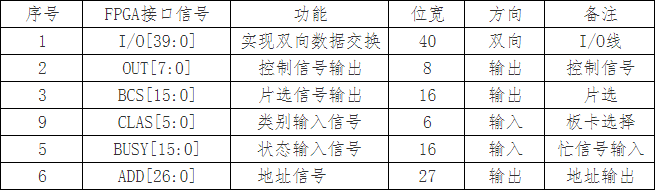

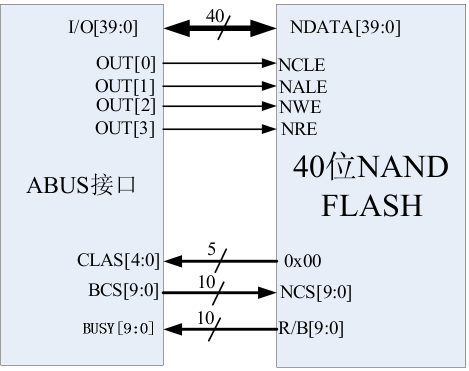

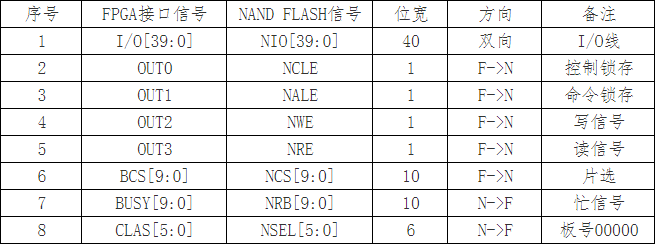

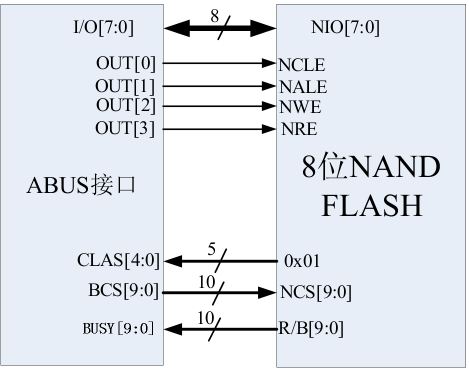

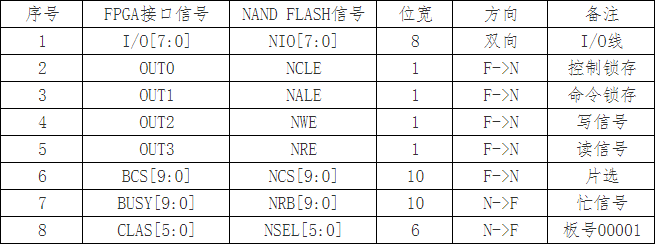

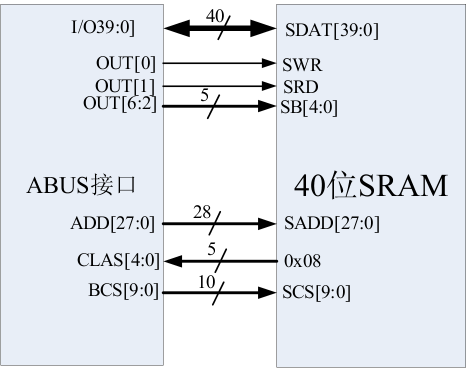

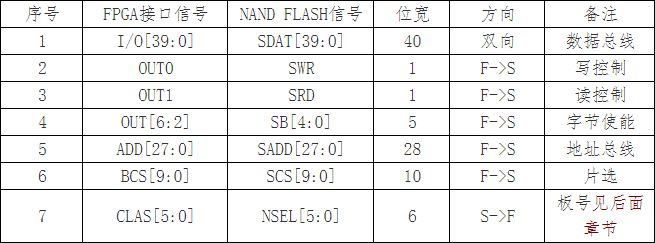

电子技术的飞速发展, 存储器的种类日益繁多,每一种存储器都有其独有的操作时序,为了提高存储器芯片的测试效率,一种多功能存储器芯片的测试系统应运而生。本文提出了一种多功能存储器芯片的测试系统硬件设计与实现,对各种数据位宽的多种存储器芯片(SRAM、MRAM、NOR FALSH、NAND FLASH、EEPROM等)进行了详细的结口

电路设计(如何挂载到NIOSII的总线上),最终解决了不同数据位宽的多种存储器的同平台测试解决方案,并详细地设计了各结口的硬件实现方法。

举报

举报

举报

举报

举报

举报

举报

举报