控制/MCU

YTM32 M系列芯片基于32位车规级ARM Cortex-M33内核,CPU全温域主频高达120MHz,提供1.25MB嵌入式闪存,符合ISO26262的ASIL-B等级要求,可靠性满足AEC-Q100、Grade1标准,信息安全方面支持AES、SHA以及国密SM4等多种加密算法,并提供符合AUTOSAR标准的MCAL。

时钟模块是嵌入式软件设计的基础,只有详细了解了嵌入式芯片的时钟结构,在实际应用中才能使芯片发挥全部的性能,同时,根据不同的应用需求,选择合适的时钟源,可以同时兼顾应用的性能需求和功耗需求,从而使系统设计更好的满足应用需求。

YTM32B1ME0系列MCU时钟模块通过SCU统一管理,芯片支持PLL,FIRC,SIRC,FXOSC以及SXOSC几种时钟源,除了SXOSC以外,其余四种时钟源都可以选择为系统时钟源。

ME系列芯片的时钟在低功耗模式下都是可以进行配置的,当在相应的低功耗模式下开启时钟,会造成该低功耗模式的功耗增加。针对不同时钟在不同低功耗模式下的具体行为列举如下:

| Run | Sleep | Deep Sleep | Standby | Power Down | |

|---|---|---|---|---|---|

| FIRC | Optional | Optional | Optional | OFF | OFF |

| SIRC | ON | ON | Optional | Optional | Optional |

| FXOSC | Optional | Optional | Optional | OFF | OFF |

| SXOSC | Optional | Optional | Optional | Optional | Optional |

| PLL | Optional | Optional | Optional | OFF | OFF |

车规芯片对于Function Safety是有很高要求的,YTM32 M系列MCU可以满足ASIL-B的安全等级要求,在时钟模块设计上,为了满足时钟的安全性需求,芯片内部集成了一个4通道的时钟监测模块CMU,可以在芯片运行过程中实时监测时钟是否稳定可靠。

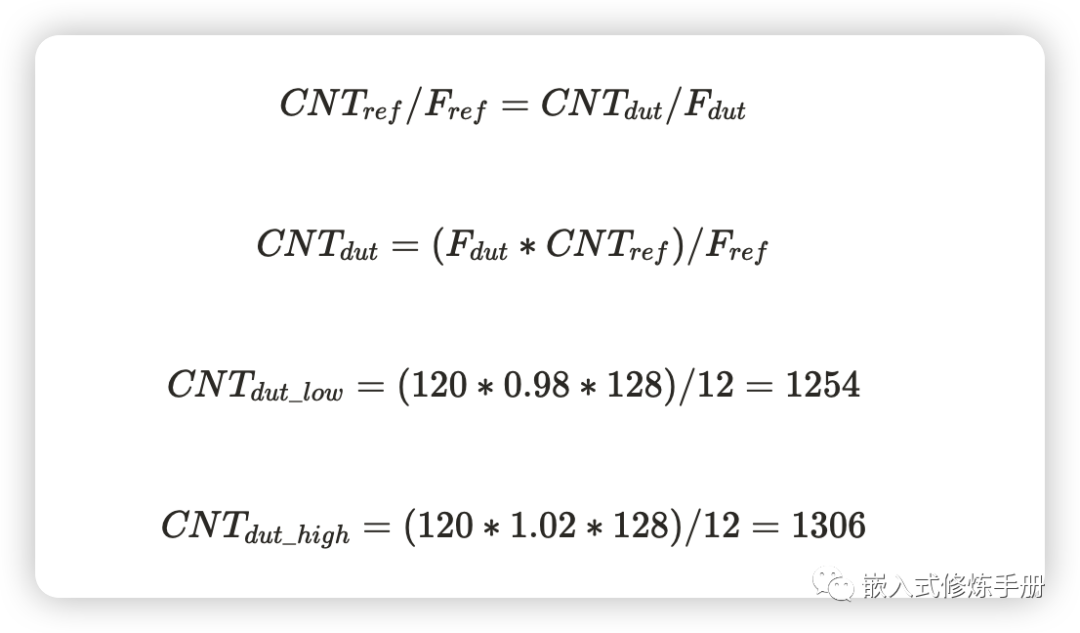

CMU的基本原理是通过时钟之间的互相监测实现对时钟工作状态的异常监测。在CMU的内部,每个监测通道同时会有两个计数器采用两种不同的时钟进行计数,其中参考时钟计数溢出值固定为128,用于可以设定被监测时钟的异常判定范围,比如采用12MHz的SIRC对120MHz的PLL输出进行监测,如果允许的频率偏差为正负2%,那么异常判定的上下限可以通过如下公式计算:

YTM32 M系列模块时钟主要有以下三种类型:

| No. | Module | Bus | Gate | Function |

|---|---|---|---|---|

| 0 | - | - | - | - |

| 1 | - | - | - | - |

| 2 | - | - | - | - |

| 3 | - | - | - | - |

| 4 | - | - | - | - |

| 5 | - | - | - | - |

| 6 | - | - | - | - |

| 7 | - | - | - | - |

| 8 | DMA | SYS_CLK | YES | - |

| 9 | - | - | - | - |

| 10 | - | - | - | - |

| 11 | - | - | - | - |

| 12 | - | - | - | - |

| 13 | - | - | - | - |

| 14 | - | - | - | - |

| 15 | TRACE | - | - | - |

| 16 | EFM | SLOW_BUS_CLK | YES(1) | - |

| 17 | GPIO | SYS_CLK | YES | YES |

| 18 | PCTRLA | SLOW_BUS_CLK | - | - |

| 19 | PCTRLB | SLOW_BUS_CLK | - | - |

| 20 | PCTRLC | SLOW_BUS_CLK | - | - |

| 21 | PCTRLD | SLOW_BUS_CLK | - | - |

| 22 | PCTRLE | SLOW_BUS_CLK | - | - |

| 23 | - | - | - | - |

| 24 | - | - | - | - |

| 25 | - | - | - | - |

| 26 | - | - | - | - |

| 27 | LINFlexD0 | SLOW_BUS_CLK | YES | - |

| 28 | LINFlexD1 | SLOW_BUS_CLK | YES | - |

| 29 | LINFlexD2 | SLOW_BUS_CLK | YES | - |

| 30 | LINFlexD3 | SLOW_BUS_CLK | YES | - |

| 31 | LINFlexD4 | SLOW_BUS_CLK | YES | - |

| 32 | LINFlexD5 | SLOW_BUS_CLK | YES | - |

| 33 | - | - | - | - |

| 34 | - | - | - | - |

| 35 | I2C0 | SLOW_BUS_CLK | YES | YES |

| 36 | I2C1 | SLOW_BUS_CLK | YES | YES |

| 37 | I2C2 | SLOW_BUS_CLK | YES | YES |

| 38 | - | - | - | - |

| 39 | - | - | - | - |

| 40 | - | - | - | - |

| 41 | - | - | - | - |

| 42 | SPI0 | SLOW_BUS_CLK | YES | YES |

| 43 | SPI1 | SLOW_BUS_CLK | YES | YES |

| 44 | SPI2 | SLOW_BUS_CLK | YES | YES |

| 45 | SPI3 | SLOW_BUS_CLK | YES | YES |

| 46 | SPI4 | SLOW_BUS_CLK | YES | YES |

| 47 | SPI5 | - | - | - |

| 48 | FlexCAN0 | FAST_BUS_CLK | YES | - |

| 49 | - | - | - | - |

| 50 | - | - | - | - |

| 51 | - | - | - | - |

| 52 | FlexCAN1 | FAST_BUS_CLK | YES | - |

| 53 | - | - | - | - |

| 54 | - | - | - | - |

| 55 | - | - | - | - |

| 56 | FlexCAN2 | FAST_BUS_CLK | YES | - |

| 57 | - | - | - | - |

| 58 | - | - | - | - |

| 59 | - | - | - | - |

| 60 | FlexCAN3 | FAST_BUS_CLK | YES | - |

| 61 | FlexCAN4 | FAST_BUS_CLK | YES | - |

| 62 | FlexCAN5 | FAST_BUS_CLK | YES | - |

| 63 | - | - | - | - |

| 64 | ADC0 | SLOW_BUS_CLK | YES | YES |

| 65 | ADC1 | SLOW_BUS_CLK | YES | YES |

| 66 | - | - | - | - |

| 67 | ACMP0 | SLOW_BUS_CLK | YES | YES |

| 68 | - | - | - | - |

| 69 | - | - | - | - |

| 70 | PTU0 | FAST_BUS_CLK | YES | - |

| 71 | PTU1 | FAST_BUS_CLK | YES | - |

| 72 | TMU | SLOW_BUS_CLK | - | - |

| 73 | eTMR0 | FAST_BUS_CLK | YES | - |

| 74 | eTMR1 | FAST_BUS_CLK | YES | - |

| 75 | eTMR2 | FAST_BUS_CLK | YES | - |

| 76 | eTMR3 | FAST_BUS_CLK | YES | - |

| 77 | eTMR4 | FAST_BUS_CLK | YES | - |

| 78 | eTMR5 | FAST_BUS_CLK | YES | - |

| 79 | - | - | - | - |

| 80 | - | - | - | - |

| 81 | - | - | - | - |

| 82 | - | - | - | - |

| 83 | - | - | - | - |

| 84 | TMR0 | SLOW_BUS_CLK | YES | - |

| 85 | - | - | - | - |

| 86 | - | - | - | - |

| 87 | - | - | - | - |

| 88 | - | - | - | - |

| 89 | - | - | - | - |

| 90 | pTMR0 | SLOW_BUS_CLK | YES | - |

| 91 | - | - | - | - |

| 92 | - | - | - | - |

| 93 | lpTMR0 | SLOW_BUS_CLK | YES | YES |

| 94 | - | - | - | - |

| 95 | - | - | - | - |

| 96 | RTC | SLOW_BUS_CLK | YES | - |

| 97 | REGFILE | - | - | - |

| 98 | WKU | - | - | - |

| 99 | - | - | - | - |

| 100 | - | - | - | - |

| 101 | CRC | SYS_CLK | YES | - |

| 102 | TRNG | SLOW_BUS_CLK | YES | - |

| 103 | HCU | SYS_CLK | YES | - |

| 104 | - | - | - | - |

| 105 | - | - | - | - |

| 106 | WDG | SLOW_BUS_CLK | YES(1) | - |

| 107 | EWDG | - | - | - |

| 108 | - | - | - | - |

| 109 | - | - | - | - |

| 110 | - | - | - | - |

| 111 | - | - | - | - |

| 112 | - | - | - | - |

| 113 | INTM | SLOW_BUS_CLK | YES | - |

| 114 | EMU | FAST_BUS_CLK | YES | - |

| 115 | - | - | - | - |

| 116 | - | - | - | - |

| 117 | - | - | - | - |

| 118 | - | - | - | - |

| 119 | STU | SLOW_BUS_CLK | YES | - |

| 120 | - | - | - | - |

| 121 | - | - | - | - |

| 122 | - | - | - | - |

| 123 | CIM | - | - | - |

| 124 | SCU | SLOW_BUS_CLK | YES(1) | - |

| 125 | - | - | - | - |

| 126 | PCU | SLOW_BUS_CLK | YES(1) | - |

| 127 | RCU | SLOW_BUS_CLK | YES(1) | - |

上表是YTM32B1ME0的时钟配置,第三列的BUS代表当前模块所属的BUS时钟域,不同的bus时钟域主要是时钟频率有差异,这个时钟域的配置用于不能更改,应用上也只需要做频率的区分就可以了,Gate代表模块支持通过IPC关闭时钟,YES(1)表示模块时钟在芯片复位之后默认开启。Function列表示模块是否支持功能时钟选择,可以看到只有部分模块支持功能时钟,对于其他不支持功能时钟选择的模块,对应的IPC时钟选择寄存器域是无法写入的。Addition列代表模块的其他时钟源,这些模块的详细配置如下:

FAST_BUS_CLK,当计算LINFlexD模块波特率的时候,需要依据FAST_BUS_CLK的频率来进行计算(MD1中LINFlexD已经支持功能时钟)FAST_BUS_CLK或者FXOSC_CLK,这部分的选择是在FlexCAN模块内部实现的。全部0条评论

快来发表一下你的评论吧 !