电子说

作为IC设计人员,熟练掌握数字前端语法检查工具Spyglass的重要性不言而喻,本文手把手教你学习Spyglass工具。

启动Spyglass软件:spyglass &

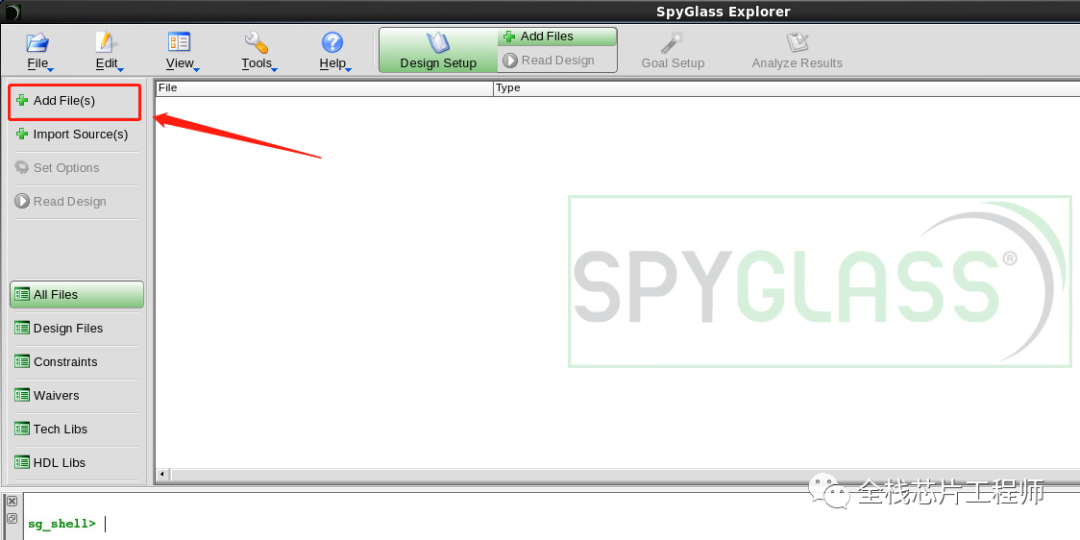

点击左边Add File(s):

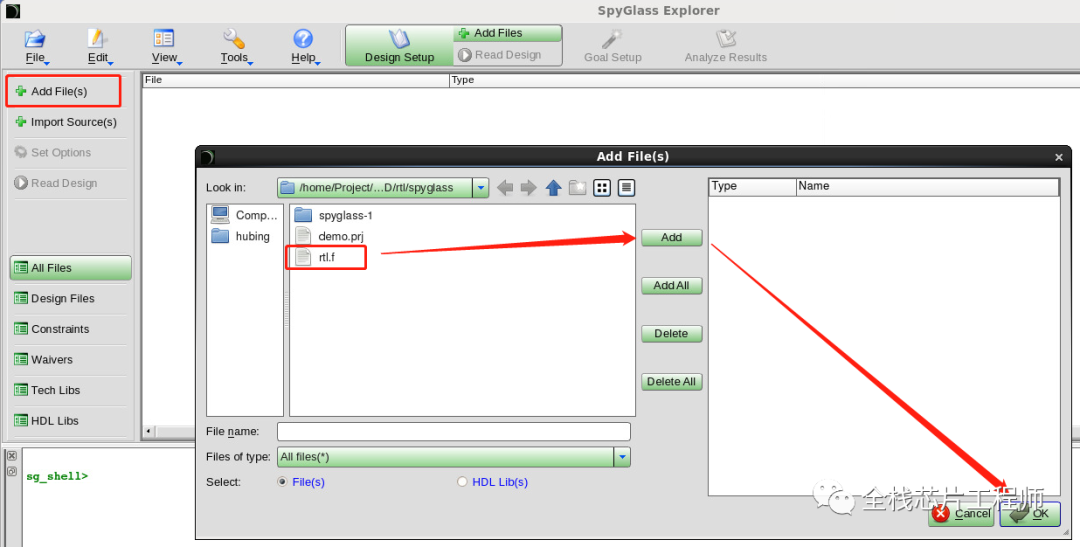

将.v文件通过rtl.f统一添加,如下图,点击OK:

或者通过命令添加:

sg_shell> read_file -type sourcelist rtl.f

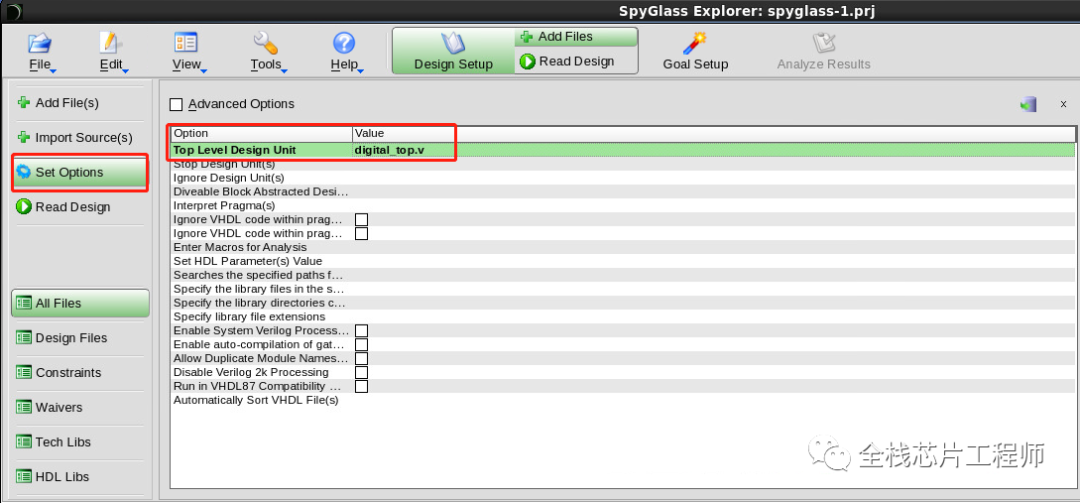

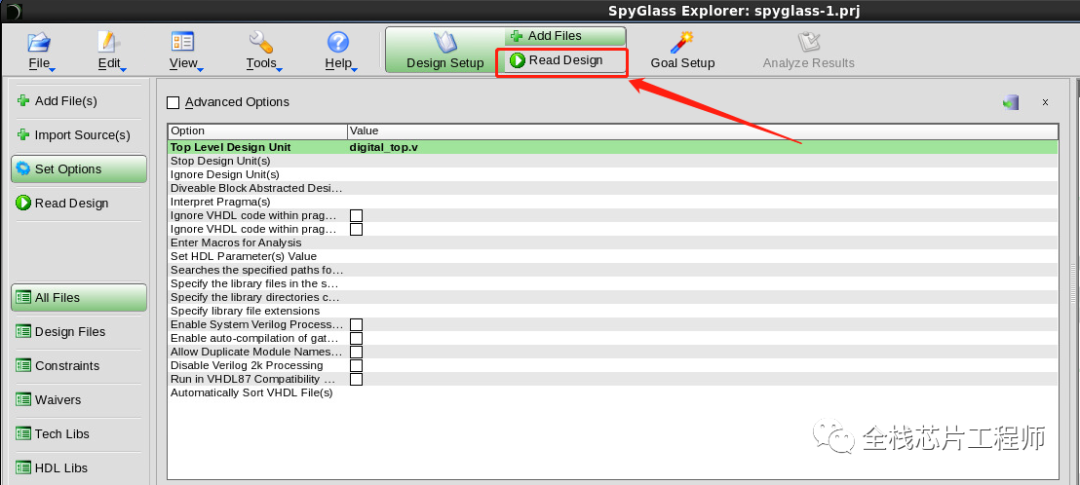

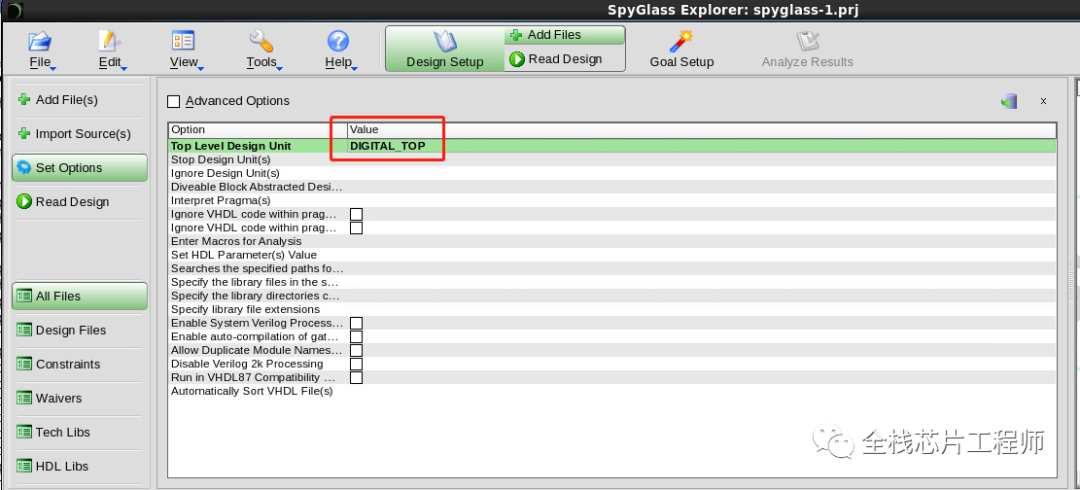

设置顶层,选中下图左边Set Options,手动设置Value为digital_top.v,这里我们留一个bug,后面看得到。

或者通过命令添加:

sg_shell> set_option top digital_top.v

我们也可以默认缺省顶层文件,此处,我们暂时不用remove_option top命令,注意刚才我们留了一个bug。

sg_shell> remove_option top

点击Read Design,

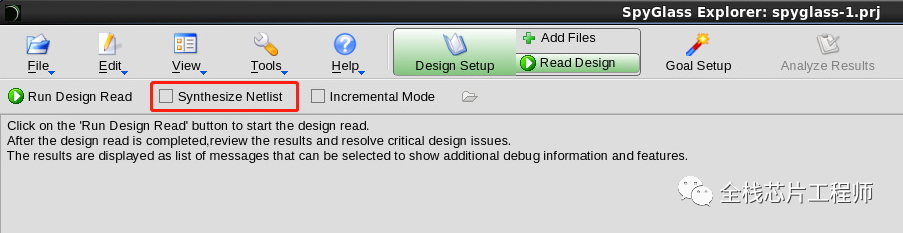

选择Synthesize Netlist,在读入设计的同时进行综合

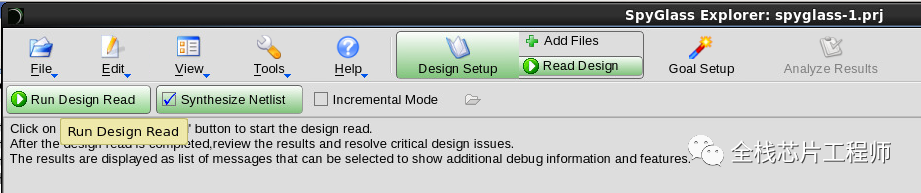

点击Run Design Read:

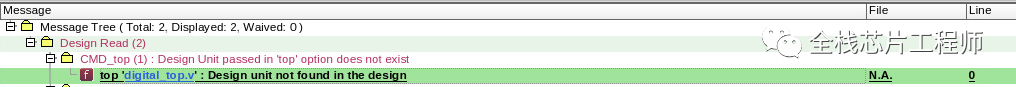

读取完成发现:

top 'digital_top.v' : Design unit not found in the design

bug来了,什么问题呢?找不到Design unit, 聪明的你一定发现了,顶层是module名,不是module文件名。如下图所示:

也就是说设置Top level Design Unit的value为DIGITAL_TOP, 而不是digital_top.v。

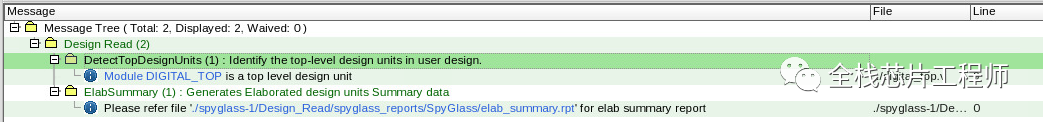

再次Run Read Design,如下图,读取成功。

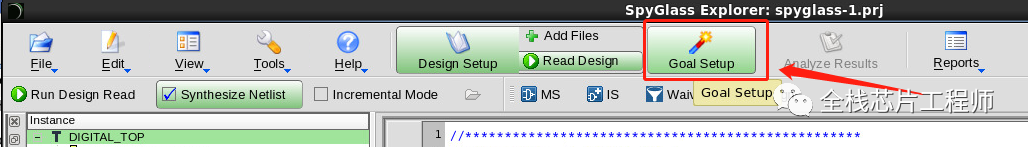

接着,设置Goal Setup:

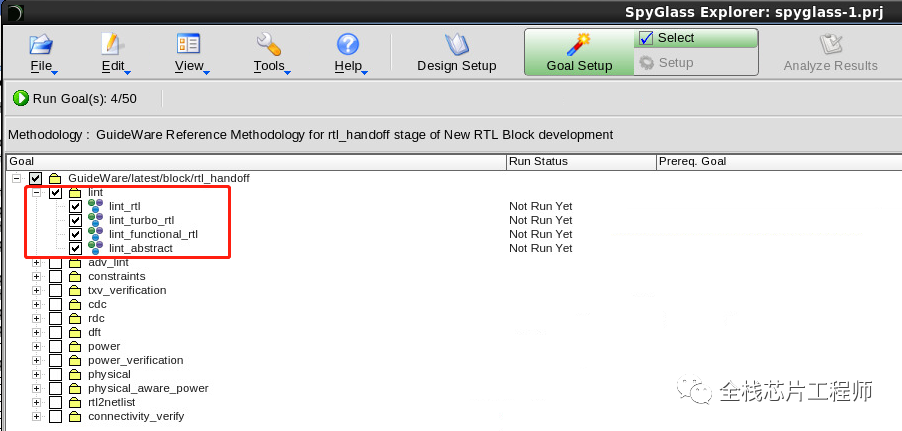

首先选中lint,我们先看lint, 点击Run Goal:

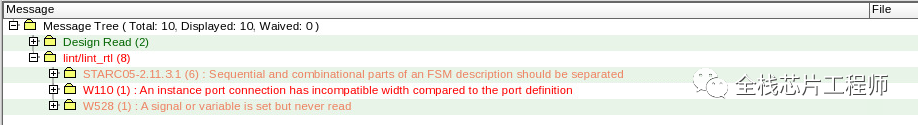

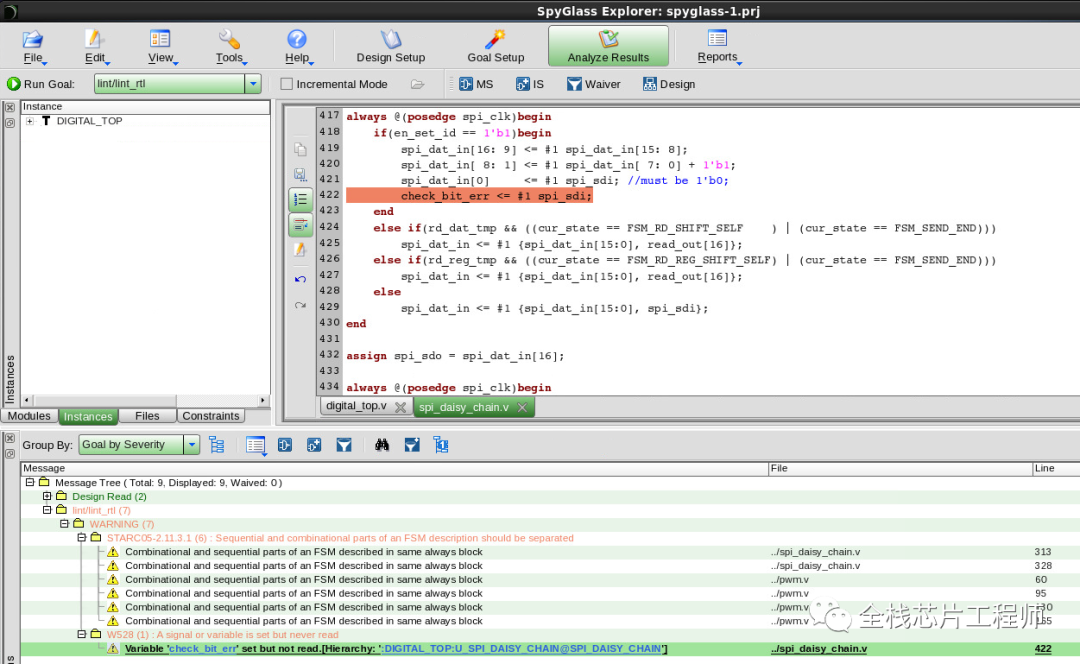

运行得到结果如下。

在看到一条条lint Warning信息后,怎么才能更清晰地知道warning的具体原因呢?告诉你一个好习惯!

Spyglass的Analyze Results默认GUI界面如下,

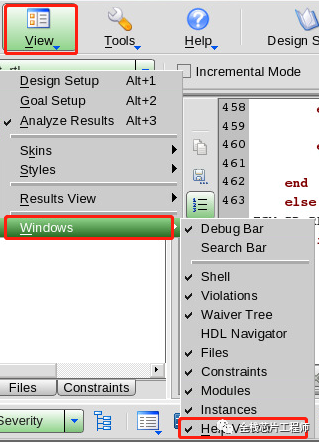

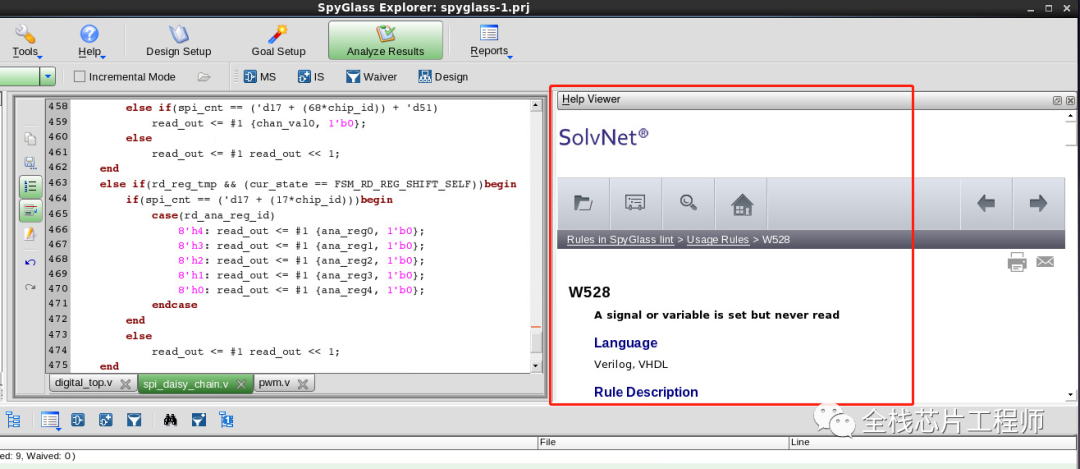

我们通过View -> Windows -> Help Viewer 来查看SolvNet对每个RTL lint warning类型的解释。

举个例子:

W528 : A signal or variable is set but never read

W528是Warning类型,说一个信号或者变量没有负载。

举个例子:

信号bigbus在第一个assign statement中被赋值了256bit位宽,但是在第二个assign statement中,bigbus仅128 bits (2**(13-7+1) 或者 2**(6-0+1)) 会被选择。因此,W528 的warning message就会出现。

module test1 (a, b);

input [13:0] a;

output [1:0] b;

wire [255:0] bigbus;

assign bigbus = {{16{4'h0}},{16{4'h0}},{16{4'h0}},{16{4'h0}}};

assign b={bigbus[a[13:7]],bigbus[a[6:0]]};

endmodule

审核编辑:刘清

全部0条评论

快来发表一下你的评论吧 !