边沿触发器

边沿触发器的特点:

在时钟为稳定的0或1期间,输入信号都不能进入触发器,触发器的新状态仅决定于时钟脉冲有效边沿到达前一瞬间以及到达后极短一段时间内的输入信号. 边沿触发器具有较好的抗干扰性能。

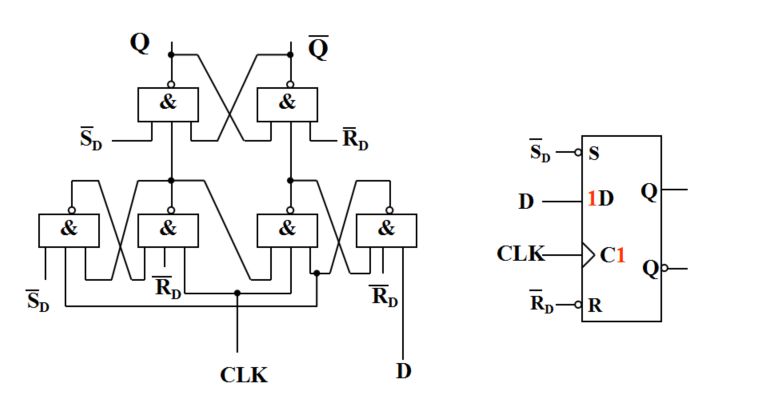

维持阻塞D触发器

(1) 电路结构与逻辑符号

(2) 工作原理

① 异步清零

② 异步置1

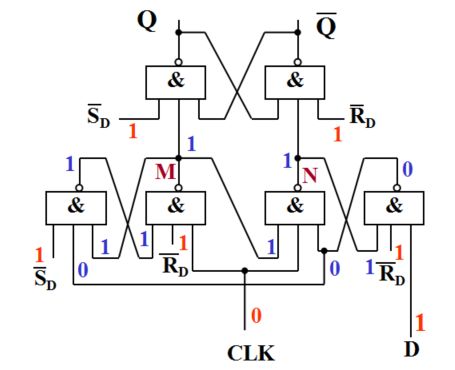

a. CLK=0

b. CLK=1

注意:在该时刻,D的改变不会使输出状态变化。

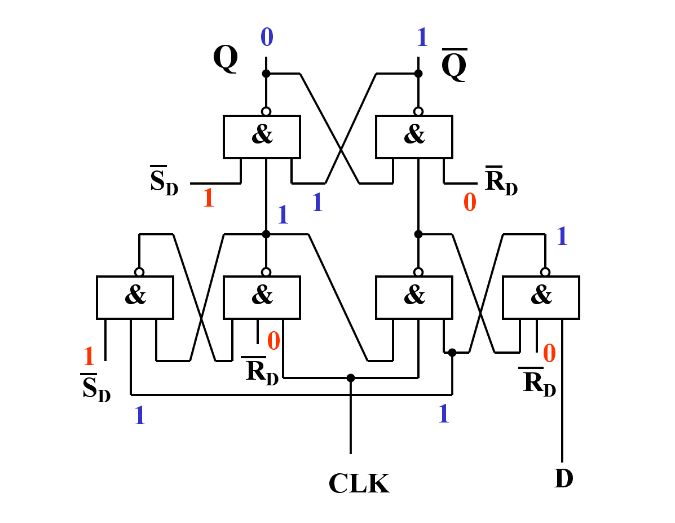

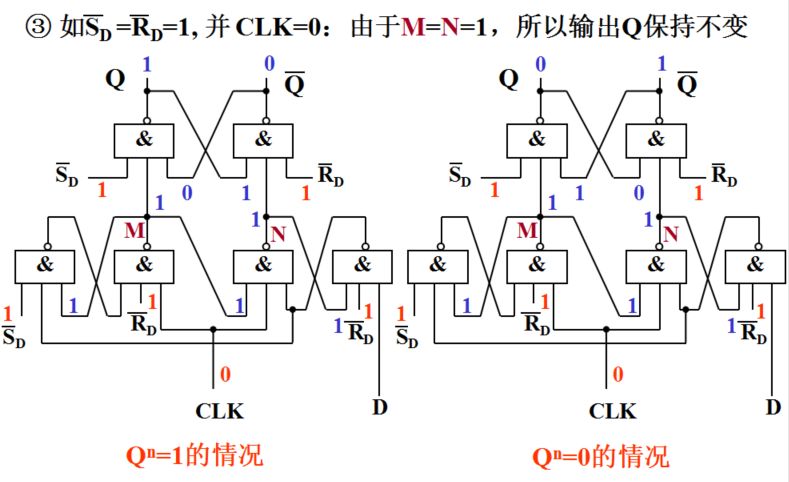

④ 在CLK=1前一瞬间(CLK=0),如加入信号D=0,则有:

由于M=N=1,所以输出Q保持不变。

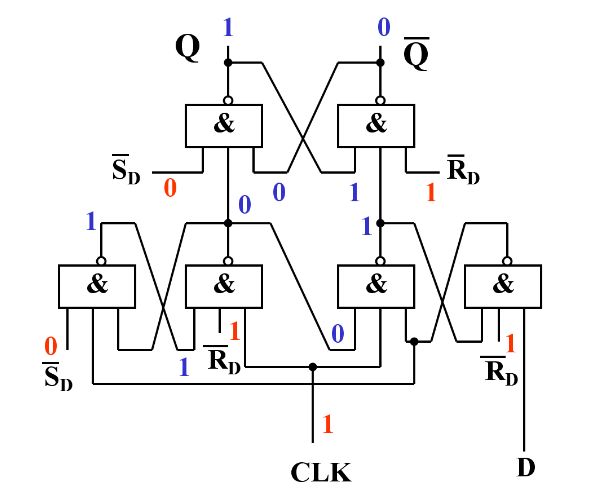

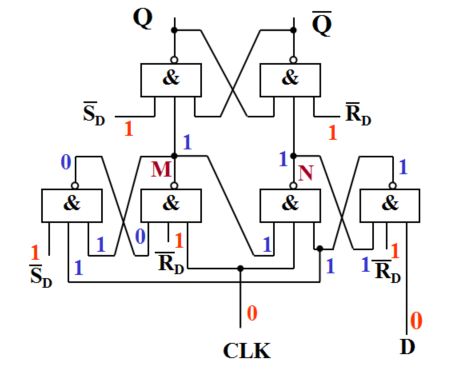

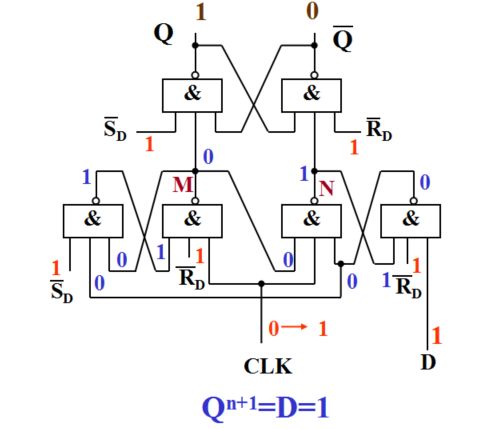

⑤ CLK由0变为1,在这一短时间内,D=0保持不变,则有:

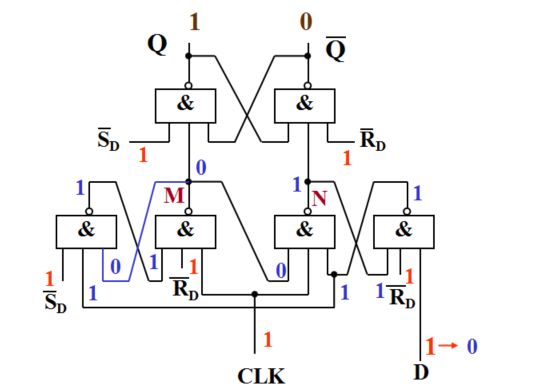

⑥ 在上面的情况下,如D发生变化,即由0变为1

由于图中红线的作用,电路输出状态保持不变。

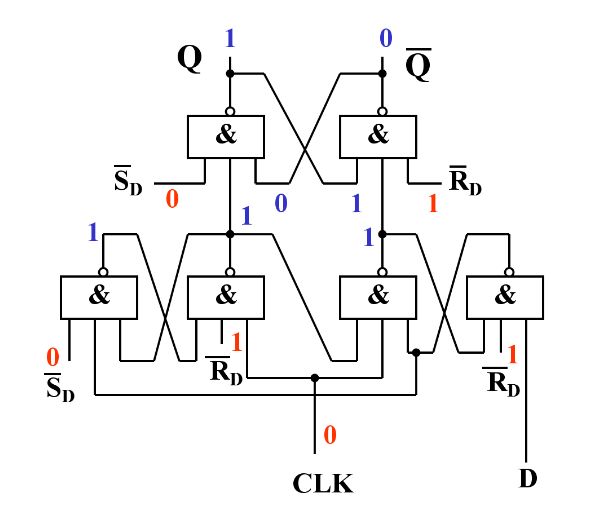

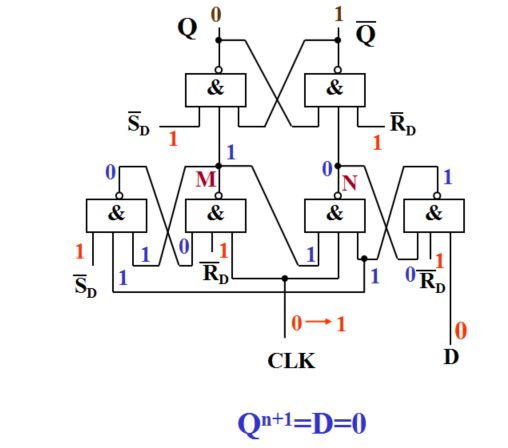

⑦ 在CLK=1前一瞬间(CLK=0),如加入信号D=1,则有:

由于M=N=1,所以输出Q保持不变。

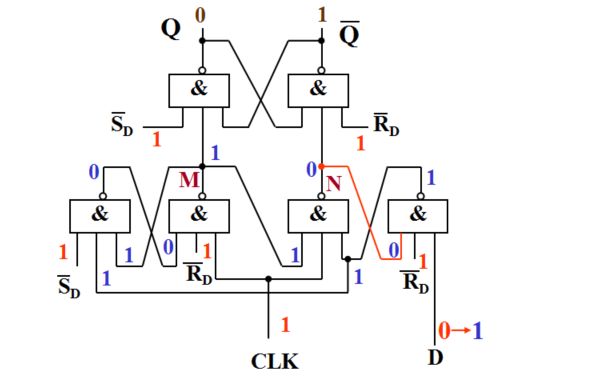

⑧ CLK由0变为1,在这一短时间内,D=1保持不变,则有:

⑨ CLK由0变为1,在这一短时间内,如D发生变化,即由1变为0

由于和M端连接的蓝线的作用,使输出保持不变

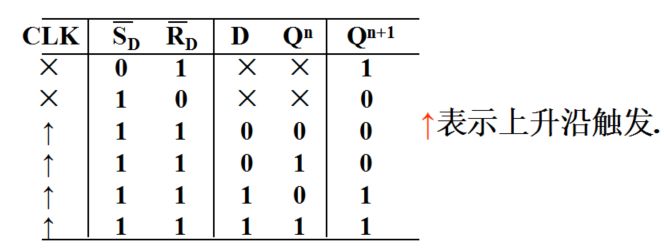

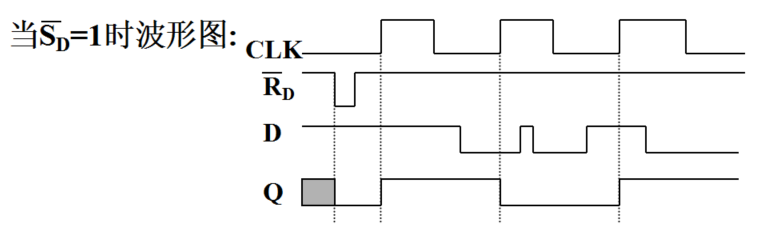

(3) 维持阻塞D触发器特性表和工作波形图

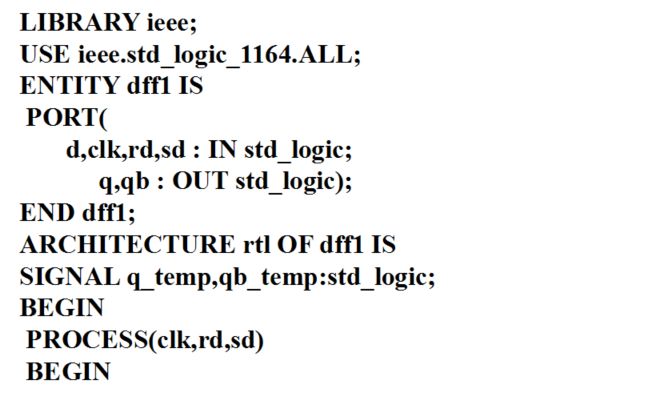

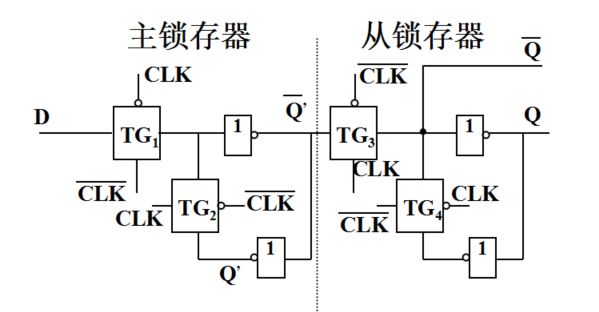

(4)正边沿 D 触发器的 VHDL 描述

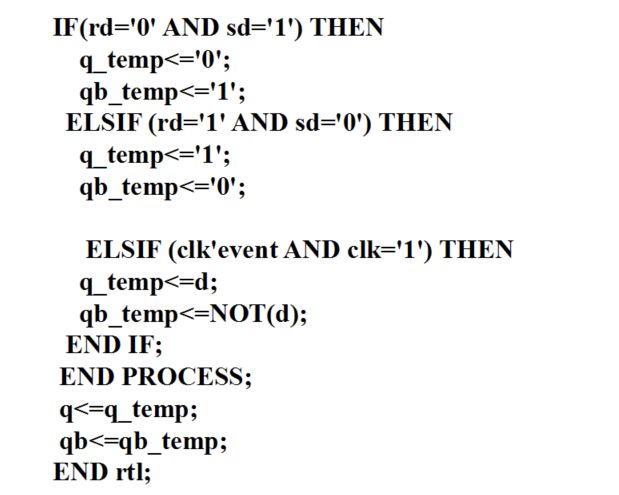

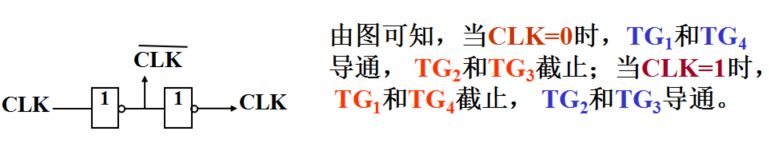

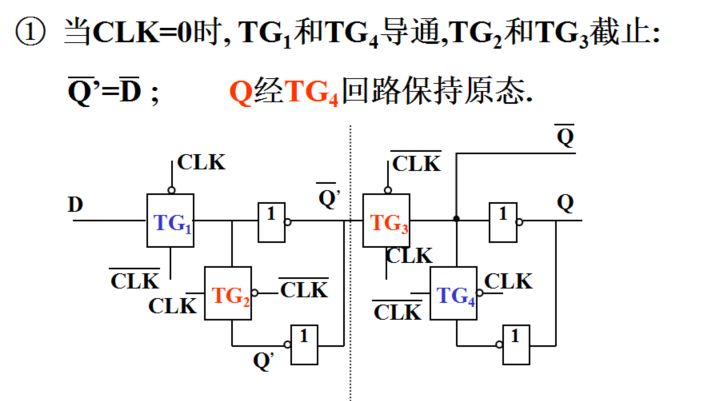

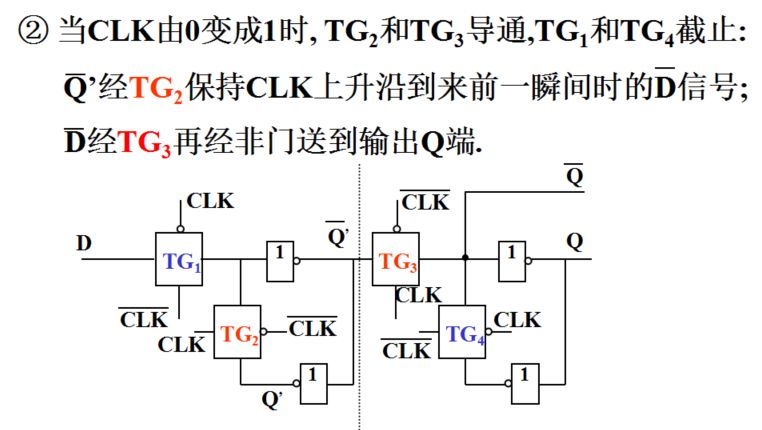

2.CMOS边沿D触发器

CMOS边沿D触发器由CMOS传输门构成,属主从结构,但具有边沿触发器的特点。

(1)电路结构

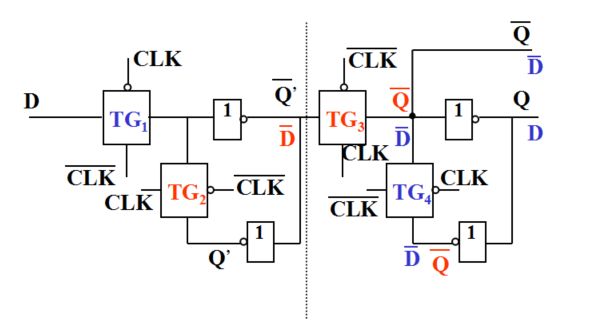

(2) 工作原理

可见,这种形式的触发器属于上升边沿触发的D触发器。

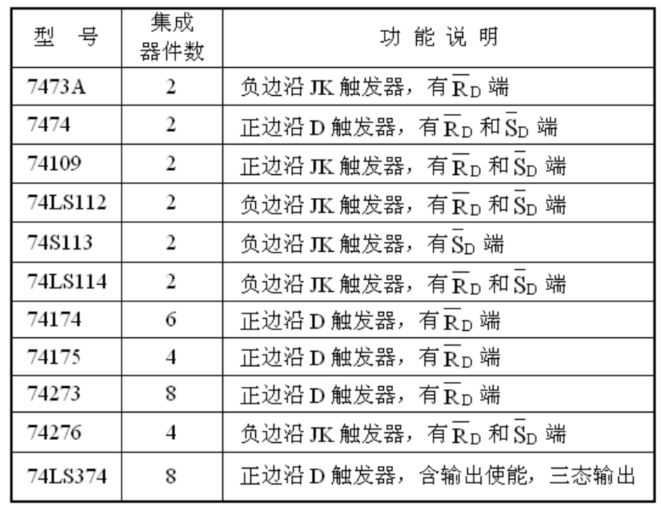

部分常用集成触发器

全部0条评论

快来发表一下你的评论吧 !