摘要

在射频超外差接收机中,下变频器是一种常用的功能组件,主要用于射频信号的侦测接收。针对 6 ~18 GHz 频段,提出一种下变频器的设计方案。下变频器采用混合集成电路工艺,中频处理带宽1 GHz,噪声系数优于6 dB,幅度一致性优于±2 dB,相位一致性优于±15°,无虚假动态范围大于50 dB。组件内部采用多功能芯片和 MEMS滤波器组,内置多级数控衰减和数控移相器。下变频器具有频段宽、体积小、集成度高、易于调试的优点。

引言

下变频器是接收系统中的核心部件,接收系统需要把高频信号用下变频器转换到低频,便于后级进行信号处理。随着半导体技术的发展,单片微波集成电路(MMIC) 突破传统的混合微波集成电路(MIC)快速发展起来。MMIC 芯片尺寸小,寄生参数少,具有优秀的高频性能。MMIC 芯片的大规模运用已成为微波组件小型化的重要途径之一 。变频器也向着小型化、高集成、低成本的方向发展。

本文介绍一种高幅相一致6 ~18 GHz 下变频器的设计方案和测试结果,该组件采用毫米波变频方案,幅度和相位都可以数控调节。组件的噪声系数优于 6 dB,无虚假动态范围大于 50 dB,组件之间幅度一致性优于±2 dB,相位一致性优于±15°。组件内部采用多功能芯片,多功能芯片集成了混频器、倍频器、低噪声放大器以及开关。本组件体积小,集成度高,调试简单,可以满足工程应用的需求。

1 下变频器方案设计

宽带下变频器设计要点是在确保噪声系数的基础上,避免带内及近边带杂散和虚假信号的产生。根据下变频的原理,一个变频器的杂散水平主要取决于以下两点:

①射频带宽和中频频率的比值; ②射频相对带宽。具体来说,射频滤波器组的通道带宽应尽可能窄,并且要尽量提高中频的频率。 下变频器的噪声系数主要取决于射频前端的增益,较高的前端增益有利于改善噪声系数; 但是前端增益越大,进入混频器的信号功率也会增大,容易引起杂散和虚假指标的恶化。在本方案里,可以根据射频频率码来统筹设置射频和中频的衰减值;即总增益保持一定的情况下,在噪声系数、虚假和杂散指标之间寻求一个最佳平衡。

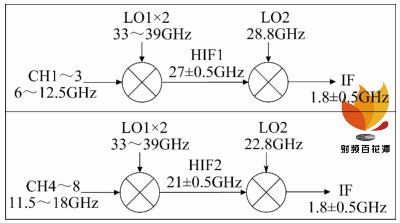

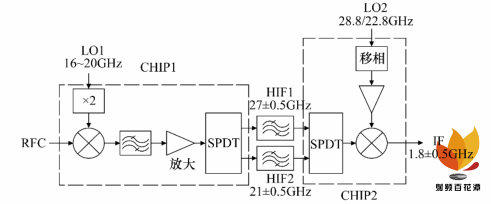

本方案中,考虑到成本和体积,6 ~18 GHz 射频信号经过开关滤波器组划分为 8 个通道。如图 1 所示,变频选择毫米波本振方案,先将6 ~18 GHz 变频至 20 GHz 以上的高中频(HIF1 和 HIF2),再下变频到低中频。为确保第一次变频后的射频二次谐波不落进带内,6 ~12. 5 GHz 和 11. 5 ~18 GHz 分别变换至 27 GHz(HIF1)和 21 GHz(HIF2)高中频,对应的一本振 LO1 频率为 33 ~39 GHz。第二次变频选择两个点频作为二本振 LO2,最终获得 1. 8 GHz 中频,瞬时处理带宽为 1 GHz。本方案中,所有的频率都不超过 40 GHz,以目前的器件水平都比较易于实现。

图 1 变频方案

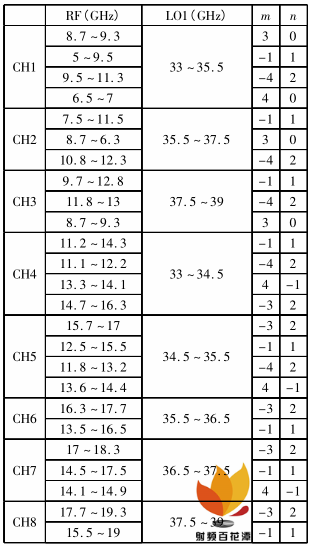

一次混频杂散计算如图 2 所示,其中 m 和 n 分别表示射频和本振的阶数。可以看出,带内及近边带没有小于 3 阶的低阶杂散。

图 2 一次混频杂散分布

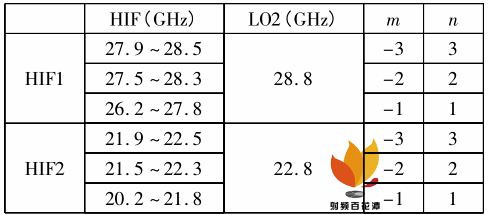

二次混频杂散如图 3 所示,只有中频的二次谐波和三次谐波组合会落入近边带,混频器对这些高阶组合的抑制度可以确保虚假和杂散指标。

图 3 二次混频杂散分布

上述论证分析表明该变频方案有效地避开了带内低次杂散。

2 具体电路实现

电路划分为三部分:射频前端,变频电路,中频电路。下面分别介绍这三部分的电路细节。

2. 1 射频前端

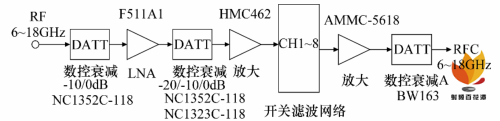

射频前端部分由低噪声放大器、数控衰减器以及 MEMS 开关滤波网络组成,如图 4 所示。两级数控衰减器,可以将 40 dB 线性动态范围扩展为 75 dB全局动态范围。射频前端的设计增益为 14 dB,噪声系数为 4 dB,输入 1 dB 压缩点为-16 dBm。这里的设计应尽量提高射频前端的 1 dB 压缩点,以减小多信号交调,提高系统对多信号的线性处理能力。

图 4 射频前端电路

2. 2 变频单元

变频 单 元 主 要 由 两 级 多 功 能 芯 片 CHIP1、CHIP2 和两路滤波器组成,如图 5 所示。第一级多功能芯片 CHIP1 集成了混频器、倍频器、单刀双掷开关、带通滤波器以及放大器。第二级多功能芯片CHIP2 集成了混频器、单刀双掷开关、移相器以及本振驱动放大器。二本振设置的移相器用来对同批次不同模块之间的相位差进行移相补偿,以确保模块之间的相位一致性。如图 4 所示,电路在混频前设置了数控衰减器 A,能够调节进入变频的信号功率。变频单元设计增益为-8 dB,噪声系数为 11 dB。

图 5 变频单元电路

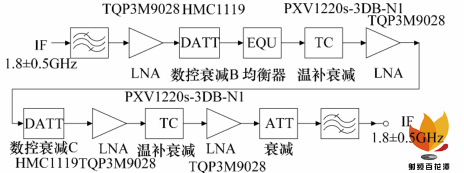

2. 3 中频电路

中频电路如图 6 所示。中频电路主要用来补偿增益、滤除杂散信号,并通过均衡器来调节中频带宽内的增益平坦度。数控衰减器 B 可以和数控衰减器 A 根据频率控制码进行联合作用。数控衰减器 C用来配合温度传感器精确补偿增益在环境温度下的变化,也可以用来调节不同模块之间的幅度一致性。中频电路的设计增益为 28 dB,噪声系数为 4 dB。

图 6 中频电路

根据上面的设计结果,对级联后的系统指标进行了仿真计算。系统总增益为 34 dB,噪声系数为5. 25 dB,满足设计指标的要求。

3 幅相一致性的调控措施

作为本设计的关键指标,幅度一致性是指组件个体之间对应于同一个射频频点(等功率输入)的中频输出功率一致性,相位一致性是指组件个体之间对应于同一个射频频点(等相位输入)的中频相位的一致性。由于射频频率被开关滤波器组划分为8 段,所以从测试结果来看,幅相一致性对应于 8 个射频频段的相位一致性。

幅相一致性设计主要靠以下几点来保证:

①射频链路中的通用器件(MMIC 芯片)需要采购同一批次产品; ②定制器件(MEMS 滤波器、LC 滤波器、腔体滤波器等)需要满足幅度和相位一致性指标; ③装配工艺中,所有装配位置都由制造工艺来定位,而非手工定位。

考虑到工程实际中幅度和相位的差值积累,电路调试手段不可缺少,本组件中设置有如下措施来调节模块之间的幅相一致性:

①在 LO2 链路上设置移相器,用于整体搬移对应的滤波器频段的相位。因为 LO2 是点频,对点频移相不用考虑频段内的相位平坦度。移相器的默认初始移相值为 90°,方便对相位的上下移动调节。 ②在中频设置低相移数控衰减器,用于调节各频段的幅度一致性。低相移的特性可以确保小幅度(≤3 dB)的校正对相位的影响微乎其微(≤2°)。

4 实物及测试结果

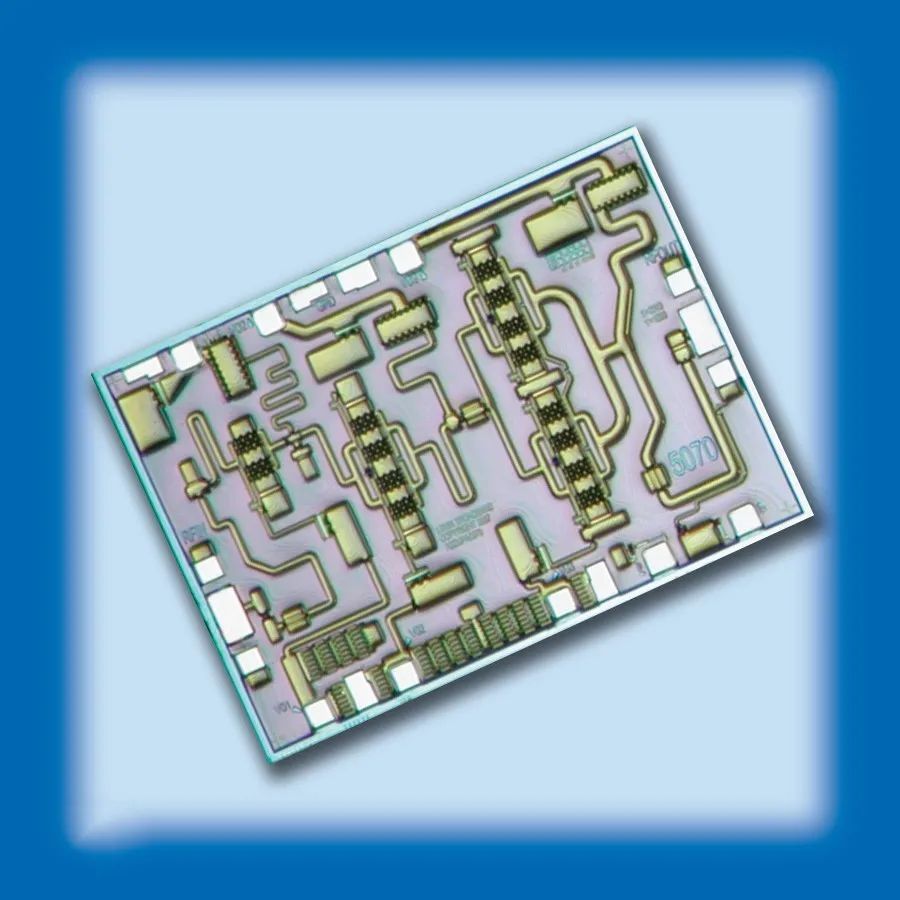

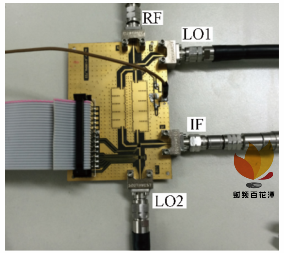

图 7 为变频单元测试板,两级变频芯片之间采用基片集成波导(SIW)滤波器。

图 7 变频单元测试板

变频器的实物尺寸为 130 mm×80 mm×20 mm,如图 8 所示。

图 8 下变频器实物图

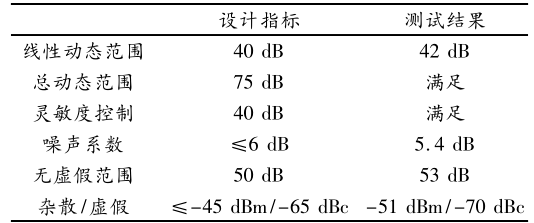

同批次模块测试结果(除幅相一致性指标外)见表 1,测试结果达到了设计指标的要求。

表 1 测试指标与设计指标对照表

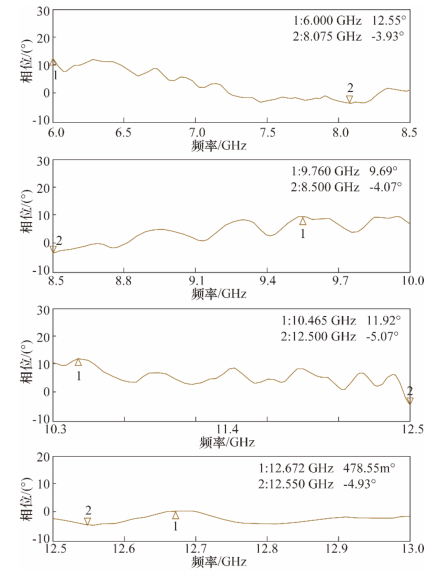

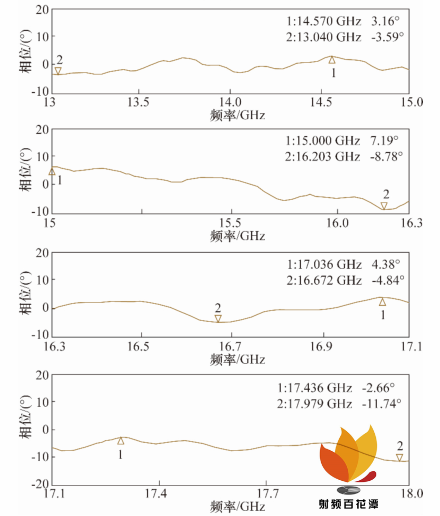

同批次模块的相位一致性测试曲线如图 9 所示,自上而下依次为 8 个射频通道的相位一致性测试曲线,可以看出,相位差值均在 20°以内,达到了设计指标(优于±15°)的要求。

图 9 相位一致性测试曲线

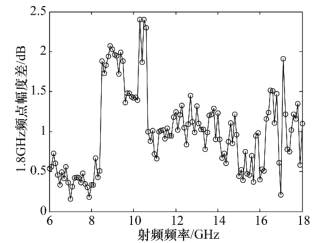

同批次模块的幅度一致性测试曲线如图 10 所示,该曲线为 6 ~18 GHz 范围内的射频频点对应的1. 8 GHz 中频幅度差值。可以看出,幅度差值均在2. 5 dB 以内,达到了设计指标(优于±2 dB)的要求。

图 10 幅度一致性测试曲线

5 结论

本文介绍了一种高幅相一致6 ~18 GHz 下变频器的设计方案和测试结果。组件内部采用多功能芯片,片上集成了混频器、倍频器、低噪声放大器以及开关。测试结果表明,组件的无虚假动态范围大于50 dB,噪声系数优于 6 dB,幅度一致性优于±2 dB,相位一致性优于±15°。本组件体积小,本组件体积小,集成度高,易于调试,可以满足工程需要。(参考文献略)

作者:张得才 管 飞 吴志亮 王洪林 陈 坤

审核编辑 :李倩

全部0条评论

快来发表一下你的评论吧 !